I just came across and interesting video from last year’s Hot Chips conference. Dr. Robert Colwell of DARPA discusses how the processor design industry is likely to change after it becomes too difficult to continue scaling transistors to ever-smaller dimensions. This is likely to occur sometime within the next decade,… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreSEMICON West 2014 Preview

There is a really big conference coming up in San Francisco…no, not DAC although of course that is coming up too. I’m talking about SEMICON West which is much bigger, filling all 3 Moscone exhibit halls. It is July 8-10th. It is, of course, the semiconductor equipment industry (and solar) show.

The opening keynote on… Read More

Mark Milligan Joins Calypto. Plus Google at DAC

I talked to Mark Milligan this morning, who has just joined Calypto as VP Marketing. I first met Mark back when he was at CoWare and I was at VaST or maybe it was Virtutech. Then he moved on and ran marketing at SpringSoft which, I’m sure you remember, Synopsys acquired. I asked him what encouraged him to join Calypto.

He said that… Read More

Methodics @ #51DAC!

This is the biggest year ever for Methodics at DAC, with lots to show, and a team of people excited to talk to customers and potential customers alike. Methodics will also be giving away Pebble Smartwatches!

Methodics theme for DAC2014 is “IP and design management done right”. A key part of this message is to show how their unique open… Read More

Dark Silicon

One of the problems with chips today is that of so-called “dark silicon”. We can put massive functionality on an SoC today. A billion transistors, and that is just at 28nm. But power constraints (both leakage and dynamic power) limit how much of the chip can be powered up at any one time. In some cases this is not that big… Read More

The Silicon ATM

One of the things that eSilicon does is handle all the backend operations for the designs that they do. eSilicon is a fabless ASIC company and so the most visible part of the business is the design (not to mention IP which is a critical input into design these days). But another key part is arranging with foundries like TSMC to get the … Read More

Cadence Go (war-game) strategy

I was attending to CDN-Live in Munich last week, so I was expecting Cadence to announce new IP related acquisition like Lip-Bu Tan did last year (Cosmic Circuit, Evatronix and Tensilica). In fact, Lip-Bu was not in Munich and Charlie Huang, SVP Worldwide Field Operations and System & Verification Group, was holding the morning… Read More

IBM and GLOBALFOUNDRIES Deal!

An interesting deal was announced last week, another piece in the What is Next for GlobalFoundries? puzzle. IBM is sending up to 200 employees from their East Fishkill R&D facility to GF’s Malta R&D center in Saratoga County. The first thing that comes to my mind is 10nm! Considering GF is licensing Samsung 14nm, what else… Read More

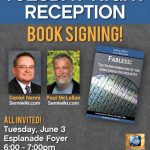

Fabless Book Giveaway at #51DAC!

The generosity of the fabless semiconductor ecosystem never ceases to amaze me. Paul McLellan and I wrote a book for the greater good and now key members of our industry will make sure that 1,500 people at this year’s Design Automation Conference will get copies. As a special thank you to all of our supporters SemiWiki will be hosting… Read More

GlobalFoundries Gets a New Manager in NY

GlobalFoundries is on the move. Of course the biggest announcement recently was the licensing of Samsung’s process to run in fab 8 in Malta, New York. This means that fab 8 will be a viable alternative, a true second source for Samsung production and one that doesn’t compete with its customers as Samsung does in many … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era