Most of the results are in for mobile for last quarter, plus the earnings calls are all over. The picture is not pretty. The big picture is that low-cost Android-based suppliers, primarily in Asia, are starting to eat a lot of market share from Samsung (#1) and Apple (#2). There were about 295M smartphones shipped in Q2, a measly 2% … Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

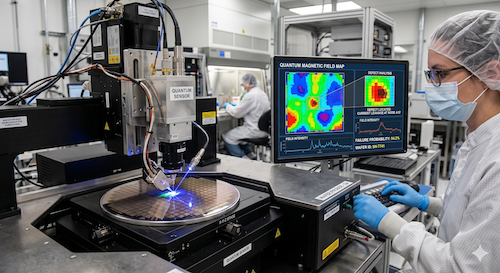

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More #DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read MoreWill Intel Have a Bigger FinFET Market Share Than TSMC in 2015?

Speculation is running rampant after last month’s conference call where Dr. Morris Chang, who is often referred to as “The Chairman”, commented that at 16nm TSMC will have a smaller market share than a major competitor in 2015. TSMC will however regain the FinFET lead in 2016 and 2017. Of course the blogosphere went crazy on this … Read More

CEVA actively preparing the future

I have recently blogged about CEVA acquisition of Riviera Waves, a very positive move to consolidate CEVA leading position of connectivity IP vendor (Bluetooth and WiFi). We know CEVA for years as being the leading supplier of DSP IP cores for the wireless phone market and it look like that we will have to rethink this definition,… Read More

The Carrington Event

Back in the pre-SemiWiki days when I had the EdaGrafitti blog I wrote about the Carrington event. This was a solar storm in 1859 that lasted for several days. On September 1st there was a coronal mass ejection (CME) traveling directly towards earth. Normally such an event would take several days to reach earth but an earlier ejection… Read More

Xilinx, 100 Reasons to use them

We all like compliments, correct? You know the kind that go like, “Glad you didn’t screw that up”. From time to time I get, “You write what you do because you’re affiliated with Xilinx”. Perhaps I will name my next child Xilinx. I have said this before, I do real work (debatable) and trade studies,… Read More

The Grand Folly of India’s Foundry Plans, Part 2

Image Source: Wikipedia

Authors: Pete Gasperini & Abhijit Athavale

The first article on this topic, published here on Semiwiki on July 6[SUP]th[/SUP], addressed New Delhi’s proposal to subsidize the construction of two silicon fabs – one in 22nm, the other in 28nm – in order to stimulate India’s high tech sector and reduce… Read More

Electronic Thermal Management through Icepak

Last week my daughter was playing some games on my Google Nexus smartphone for a while when one of my friends called. When I picked up the phone, I couldn’t imagine it was so hot. There is no doubt; every electronic device today emits an order of magnitude higher heat than what it used to at most a decade ago. There is so much emphasis on … Read More

Bring Water to those in the World that need it

Dear Reader, I need your help with something.

Invention is the Mother of necessity. When I bought the Miller Farm, it came with a very shallow well. What that meant is priming the pump, alot. Me being an engineer weighed the options. The wife, with 5 kids to bath, wash clothes, cook, etc.. was a bit overwhelmed. Of course the worst day… Read More

Open Source Verilog

Over the years there have been various open source EDA projects but none that has realized a full industrial strength design tool that has broad adoption and is strong enough to compete with similar products from the EDA industry.

Open source is clearly a great way to develop software. Lots of people can see all the source code and … Read More

Enabling Higher Level Design Automation with Smart Tools

Although design houses have always strived for optimizing best design flows according to their design needs by customizing the flows using effective and efficient internal as well as external tools, this need has further grown in the context of design scenarios getting wider and wider from transistor, gate and RTL to system level.… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior