Well today, i’m easing my way back in from vacation. Took a camper, 6 kids, 1 wife with bun in the oven and saw the great USA. 17 States, roughly 5500 miles. It was great fun and tiring at the same time. The Grand Canyon was a blessing but I really enjoyed the ‘The Four Corners‘ where UT, CO, NM, AZ all meet. I had each kid… Read More

Ravi Subramanian on Trends that are Shaping AI at SynopsysRight before the Synopsys Converge Keynote I caught…Read More

Ravi Subramanian on Trends that are Shaping AI at SynopsysRight before the Synopsys Converge Keynote I caught…Read More Axiomise Introduces nocProve to Transform NoC Design VerificationAxiomise has recently launched a new verification tool…Read More

Axiomise Introduces nocProve to Transform NoC Design VerificationAxiomise has recently launched a new verification tool…Read MoreDesigning Hardware with C++ and its Advantages

Very recently, I was seeing intense discussions on the need for agile hardware development just like agile software and ideas were being sought from experts as well as individuals. While in software world it has already evolved, in hardware world it’s yet to see the shift in paradigm. My point is that the end goal of agile hardware… Read More

The IoT and the Forbidden Fruit

A tremendous froth of press and promotion has arisen in the last year concerning the Internet of Things. Nearly every High Tech firm on the globe has begun to advertise their offerings as an integral part of it, positioning their products and services as both essential to the IoT and as a vital component of its future. As the smartphone… Read More

Cliff Hou at TSMC OIP

I attended Cliff Hou’s keynote at TSMC OIP Forum earlier this month. OIP is a huge undertaking. It currently has over 100 ecosystem partners, 10 technology generations, 7600+ IPs, 60+ EDA tools, 7000+ tech files and 150+ PDKs.

Most of Cliff’s presentation gave details on where TSMC are with the various processes. … Read More

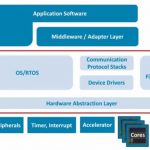

3 reasons to focus on hardware dependent software

Why is software for modern SoCs so blasted expensive to develop? One reason is more software is being developed at the kernel layer – hardware dependent software, or HdS. Application software often assumes the underlying hardware, operating system, communication stacks, and device drivers are stable. For HdS, this flawed assumption… Read More

Sensing, Processing and Connecting: IoT Fundamentals

Internet of Things, or Internet of Everything, is certainly the buzzword of the year. Does IoT describe one product family? Not really as the acronym describes a family of concepts, each of these concepts could effectively be turned into a family of products, if this concept reach the market, or fulfill a market need. Nevertheless… Read More

A Brief History of ASTC and VLAB Works

When I worked for VaST our engineering was in Sydney Australia. To my surprise there was another, entirely independent, group working on virtual platform modeling and tools in another place in Australia, in Adelaide. Is there something in the Fosters? They had originally been part of Motorola Corporate R&D and Software Group,… Read More

ANSYS Electronics Simulation Expo – A View from Industry

As we are seeing more and more automation in most of our activities, not only through software but also smart electronics (at cutting-edge technologies) equipped with processors, micro-controllers, sensors and so on which make a whole system as an integrated entity on a small piece of semiconductor intertwined with other systems… Read More

eSilicon Creates One-Click Access to MPW and GDSII Quoting Portals

I have written before about eSilicon taking their internal quoting tool and making it user accessible. This first started just for MPW shuttles for half-a-dozen foundries, and then was extended to cover production runs at TSMC. And it is getting heavily used; eSilicon have had 315 people register to use it from 43 different countries… Read More

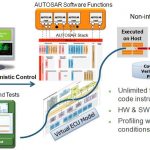

Virtual Platform Powers AUTOSAR Software Development

As a significant part of our life is spent in travelling, it’s natural that automotive sector continues to get traction with a significant push towards electronics and automated solutions for automobiles such as cars to provide safety, comfort and entertainment. These solutions are provided by complete systems which operate… Read More

Breker Hosts an Energetic Panel on Spec-Driven Verification