Imagination Technologies has designed a complete environment to address the needs of emerging IoT and other connected devices, FlowCloud. The technology has been engineered by Imagination to optimize device to cloud connectivity for embedded applications. FlowCloud is a cloud based application independent development… Read More

Reachability in Analog and AMS. Innovation in VerificationCan a combination of learning-based surrogate models plus…Read More

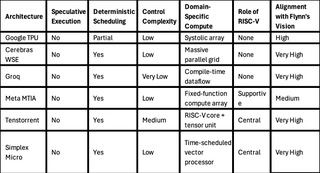

Reachability in Analog and AMS. Innovation in VerificationCan a combination of learning-based surrogate models plus…Read More Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural PivotIn 2003, legendary computer architect Michael J. Flynn…Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural PivotIn 2003, legendary computer architect Michael J. Flynn…Read More Enabling RISC-V & AI Innovations with Andes AX45MPV Running Live on S2C Prodigy S8-100 Prototyping SystemQualifying an AI-class RISC-V SoC demands proving that…Read More

Enabling RISC-V & AI Innovations with Andes AX45MPV Running Live on S2C Prodigy S8-100 Prototyping SystemQualifying an AI-class RISC-V SoC demands proving that…Read More DAC News – A New Era of Electronic Design Begins with Siemens EDA AIAI is the centerpiece of DAC this year.…Read More

DAC News – A New Era of Electronic Design Begins with Siemens EDA AIAI is the centerpiece of DAC this year.…Read MoreIntel 14nm is NOT in Production Yet!

Okay, maybe I’m the only one questioning Intel 14nm yield but I think it will be an interesting discussion in the comments section. Here are the questions I would have asked Intel during their recent 14nm PR tour: Has the P1272 process been rolled out to the production fabs in OR, AZ, and Ireland? Is the process officially in production… Read More

FD-SOI at 14nm

At the recent Semicon West, Michel Haond of ST Microelectronics had a presentation on 14nm FD-SOI, or what they more lengthily call UTBB FD-SOI (which when you expand it all out comes to Ultra Thin Body and Buried-Oxide Fully Depleted Silicon on Insulator). When Chenming Hu (or whoever in his group) came up with the term FinFET it … Read More

Another debug view in the UVM Toolbox

One of the biggest endearing qualities of a debug environment for any type of coding is availability of multiple ways to accomplish a task. Whether the preference is keyboard shortcuts, mouse left-click drill-down and right-click pull-down menus, source code view, hierarchical class view, or graphical relationship view, … Read More

How to Reduce Maximum Power at RTL Stage?

Of course that reduction has to stay throughout the design cycle up to layout implementation and fabrication. Since the advent of high density, mega functionality SoC designs at advanced nodes and battery life critical devices played by our fingertips, the gap between SoC power requirement and actual SoC power has only increased.… Read More

Cadence Completes Power Signoff Solution with Voltus-Fi

You probably remember Cadence introduced Voltus towards the end of last year at their signoff summit. This was aimed at digital designers. Prior to that they had announced Tempus, their static timing analysis tool. More recently they announced Quantus QRC extraction. All of these tools that end in -us have been re-architected… Read More

A Deeper Insight into Quantus QRC Extraction Solution

Last month Cadenceannounced its fastest parasitic extraction tool (minimum 5 times better performance compared to other available tools) which can handle growing design sizes with interconnect explosion, number of parasitics and complexities at advanced process nodes including FinFETs, without impacting accuracy of … Read More

When TSMC advocates FD-SOI…

I found a patent recently (May,14 2013) granted to TSMC “Planar Compatible FDSOI Design Architecture”, the following sentences, directly extracted from this patent, advertise FDSOI design better than a commercial promotion! “Devices formed on SOI substrates offer many advantages over their bulk counterparts, including… Read More

Transaction-based Emulation

Verification has been going through a lot of changes in the last couple of years. Three technologies that used to be largely contained in their own silos have come together: simulation, emulation and virtual-platforms.

Until recently, the workhorse verification tool was simulation. Emulation had its place but limits on capacity… Read More

Intel Versus TSMC 14nm Processes

Intel has begun to release some details on their 14nm process. I thought it would be interesting to contrast what Intel has disclosed to TSMC’s 16nm process disclosure from last year’s IEDM (TSMC calls their 14nm process 16nm).

[TABLE] align=”center” border=”1″

|-

| style=”width: 141px”… Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot