Transportation sector is growing, and we can already see that a fleet of autonomous, shared vehicles – connected to the road infrastructure, to the Internet and to a broader network of public transit options – will create incredible value. The transport sector is trying its level best to improve the safety, reliability, and cost… Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read More

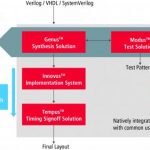

Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read MoreCadence Adds New Dimension to SoC Test Solution

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

Updated tool cuts through DO-254 V&V chaos

Audits. The mere mention of the word keeps project managers up at night and sends most designers running. However, in the case of FPGA designs seeking DO-254 compliance, the product doesn’t ship until the audit is complete – there is no avoiding it, or skating around it.… Read More

Parking Obsessed in 2016

There’s a $20B problem facing drivers in U.S. cities – in fact, it affects drivers in cities all over the world. It is the challenge of locating an available and legal parking space.… Read More

Expanding 3D EM Simulation Access to All

James Clerk Maxwell’s eponymous equations are the basis for simulating electromagnetic wave propagation. In school, EE majors tended to fall into two camps: (a) those that thoroughly enjoyed their fields and waves classes, who liked doing surface integrals, and who were adept at demonstrating the “right hand rule”, and (b) … Read More

Submerging the Data Center

One of NetSpeed’s customers is a Tier-1 semiconductor company that develops some of the industry’s best performing and most complex system on chips (SoC) for the data center and cloud computing markets. To keep its leadership in the data center market, the company needs to produce best-in-class SoC solutions year after year. … Read More

Keeping an ‘Open’ Mind with Technology

Software and hardware vendors are developing proprietary products and technologies to tap into the massive potential business opportunity with Internet of Things (IoT). While most of the noise is around consumer driven IoT, commercial applications for IoT are making huge financial impact in many verticals. Buildings alone… Read More

Smartphone-based Connected Health Insights from Patents

US20150124067 illustrates an improved technique for monitoring human health vitals without contact using the physiological signals extracted from video images captured by a video camera of a smartphone. One advantage of the contact-less vitals monitoring technique is the avoidance of contact measurement which can be a problem… Read More

HSPICE – 35 and looking good!

A maturetool. A legacytool. A tool that’s a little long in the tooth. We have all used these terms to refer to an EDA product that has not been able to keep up with technical challenges of model complexity, performance, or new features required by current SoC and system design requirements.… Read More

Where There’s Apple, There’s a Way

With hundreds of billions of dollars overseas and ridiculous profits domestically it is safe to say that Apple can have its way with whatever industry, market or project it sets its mind to. The only sad thing is that money alone can’t cure cancer or bring Middle East peace. Money can, however, help bring a new car company into… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?