IoT and the Edge Computing Paradigm – Why Edge Computing? In previous chapters we illustrated how cloud computing enables nowadays IoT applications to benefit from its capacity, scalability, elasticity and pay-as-you-go nature. During recent years a number of IoT/cloud deployments have demonstrated the merits of integrating… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read MoreObama’s greatest legacy may be the global entrepreneurship he sparked

It is rare to go to a government event, especially where political leaders are speaking, in which you can stay awake or be truly inspired. Indeed, I had very low expectations of President Obama’s Global Entrepreneurship Summit (GES), which was held at Stanford University last week. I thought it would be nothing more than a publicity… Read More

No Turning Back on Autonomous Driving

Politicians will tell you that Fridays are reserved for announcements (defeats, resignations, indictments) intended to be ignored or lost in the end of week news sink. In that context, the Friday before the U.S. Fourth of July three-day weekend may be regarded as second only to the Friday before Christmas as an ideal opportunity… Read More

Semiconductors out of step with electronics

The global semiconductor market has been on a decline (three-month-average change versus a year ago) since July 2015 according to World Semiconductor Trade Statistics (WSTS). Although numerous factors affect the semiconductor market (capacity and utilization, prices, inventory levels) in the near term, the long term growth… Read More

21 months lining up OPNFV-on-ARM for telecom

Telecom infrastructure is one area where X86 architecture hasn’t dominated historically. Infrastructure gear is spread across MIPS, Power, and SPARC architectures, with some X86, and a relative newcomer: ARM, already claiming 15% share. That’s a stunning figure considering only a bit less than 5 years ago… Read More

A Brief History of Platform Design Automation

Two weeks ago I spoke on the phone with Albert Li, Founder and CEO of Platform DA about his EDA company. Prior to founding Platform DA in Beijing, Li worked at Accelicon which was acquired by Agilent in December 2011. Mr. Li graduated from Tsinghua University and Vanderbilt University, both in Electrical Engineering, and has written… Read More

Brexit and Semiconductors

Interesting news last week with 51.9% of British voters saying yes to Brexit (exiting the European Union). What does it have to do with semiconductors? Plenty! After reading the media’s take on the subject and talking to friends (experts) in China, Taiwan, and Hong Kong, I must say that there is not a consensus to be found and there… Read More

Synopsys Launch EV6x Vision Processor… Challenging the Competition!

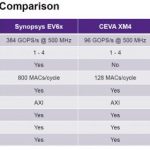

When Synopsys bought Virage Logic in 2010, ARC processor IP was in the basket, but at that time ARC processor core was not the most powerful on the market, and by far. The launch of EV6x vision processor sounds like Synopsys has moved ARC processor core by several orders of magnitude in term of processing power. EV6x deliver up to 100X… Read More

Software Security is Necessary but NOT Sufficient

As the silicon designs inside the connected devices of the Internet of Things transition from specifications to tapeouts, electronics companies have come to the stark realization that software security is simply not adequate. Securing silicon is now a required, not optional, part of RTL design processes.… Read More

From Zero to IoT Prototype in One Month

The best things in life may not always be free, but they don’t have to be incredibly difficult to get to. A challenge for IoT designers has been that their bubbling excitement over the potential of their new gizmo is quickly tempered by the complexities of actually building the hardware. Not exactly what they have come to expect in … Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!