You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

What if we all looked at driving as less of a right and more of an addiction, a disability, or a disease to be avoided, cured or overcome? What if driving were seen as a menace to society draining lives, money and time from the economy? What would our public policy priorities become in this new context?

Sweden isn’t waiting to find… Read More

The CIA, NSA, and Pokemon Go?by Kevin Kostiner on 09-23-2016 at 12:00 pmCategories: Mobile

So it’s finally out, the truth about Pokemon Go (and probably the rest of the app based mobile gaming world) and it’s a shocking, painful truth that will pretty much destroy the industry and force people back to their sedentary, solitary lives in front of their computers. And just as the average weight of an American … Read More

IoT solution development is complex. In many cases, development entails combining expertise from a number of different areas such as embedded system engineering, connectivity solution design, big data handling, application development, and data encryption techniques. Each area demands a specific array of competences … Read More

Modern SoC designs can use billions of transistors where transistors are grouped into gates, then gates grouped into cells, then cells grouped into blocks, blocks grouped into modules, and so on, creating a complex hierarchy. What a front-end designer conceives of logically for a hierarchy will differ from how an optimized physical… Read More

Electronic system level (ESL) modeling for system architecture exploration is rapidly gaining momentum. The simulation performance requirements for hardware/software co-design are demanding — an abstract model for SoC IP cores is required. Typically, soft IP will include a number of model configuration parameters.… Read More

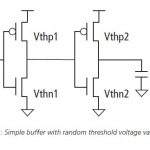

Variation is still the tough nut to crack for advanced process nodes. The familiar refrain of lower operating voltages and higher performance requirements make process variation an extremely important design consideration. As far back as the early 2000’s design teams have been looking for a better approach to model variation… Read More

“Data management tools? We use small teams doing small designs. Each project only has two or three designers. Everyone uses the same EDA tools. Why do we need another tool for collaboration?” Good question. If you enjoy frequent meetings and redoing work because someone didn’t understand the status of IP blocks, the answers may… Read More

Design starts are the lifeblood of the semiconductor industry which is why we have been following the eSilicon STAR Platform since its introduction with great anticipation. The STAR platform was first launched about three years ago. Today, there are over 1,300 registered STAR users in 52 countries around the world.

The ASIC business… Read More

Most of what you have read about design for low power has probably focused on mobile devices where power consumption constraints tend to outweigh performance objectives. These devices use aggressive power switching strategies, based on the reasonable assumption that parts or all of the device can be powered down at any given … Read More

Last week Renesas Electronics announced an agreement to acquire Intersil Corporation for US$3.22 billion. This follows July’s announcement that Analog Devices Inc. (ADI) will acquire Linear Technology Corp. (LTC) for $14.8 billion. These deals will cause a shakeup in the analog IC market. According to IC Insights ranking … Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior