A few weeks ago we previewed a Synopsys webinar describing how they are linking the ARM Juno Development Platform with the HAPS-80 and HAPS ProtoCompiler environment. I’ve had a look at the archived event and have some additional thoughts.… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreThe Package Assembly Design Kit (PADK)… the start of something big

Integrated wafer-level fanout (WLFO) packaging technology is emerging as a foundation for multi-die solutions. Mobile product applications require focus on both aggressive chip-to-chip interface performance, as well as the final package volume. Traditional multi-chip packages using PCB laminate substrates do not readily… Read More

Foundation IP for Automotive: so Stringent Quality Requirements!

The Automotive IC market is not the largest segment, but is certainly the segments expected to grow with the highest CAGR, with 10.8% from 2013 to 2018, according with IC Insights (January 2015). If you consider the pretty long concept/design to production cycle time (7 years or more) as well as the numerous segments just emerging… Read More

If an Intel 10nm transistor fell in the ARM forest

Intel’s news at IDF this week about partnering with ARM for foundry services on 10nm set off some wild speculation. It’s not a surprise that ARM would enable Intel – they’ve worked together before, ARM is an equal opportunity ecosystem partner, and ARM has publicly announced 10nm cores taped out at TSMC.… Read More

Score 1 for IDMs vs Fabless Intel King of the Photonics Hill in Data Centers

For those of you waiting with baited breath to see the Fabless community with the likes of Broadcom or Qualcomm challenge Intel in the data center space, you were just dealt a significant blow. Intel debuted their long awaited silicon photonics modules for what they called “lightning-fast” connectivity in data centers. Intel … Read More

Why is Jet-Lag Worse Flying East?

Anyone who travels long distances frequently is painfully familiar with this problem, but you may be wondering why I am mentioning it in this forum. The American Institute of Physics has a Chaos journal which looks at interdisciplinary problems in non-linear dynamics and recently published an article on just this topic.

There… Read More

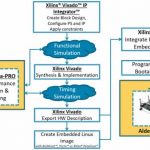

Optimization and verification wins in IoT designs

Designers tend to put tons of energy into pre-silicon verification of SoCs, with millions of dollars on the line if a piece of silicon fails due to a design flaw. Are programmable logic designers, particularly those working with an SoC such as the Xilinx Zynq, flirting with danger by not putting enough effort into verification?… Read More

Semiconductors negative in 2016, positive in 2017

Note: the table and text below have been revised from an earlier post to correct the numbers for STMicroelectronics.

Semiconductor companies posted a wide range of results in 2nd quarter 2016. Intel, Micron Technology and Renesas Electronics all had declines in revenue in 2Q 2016 versus 1Q 2016. Samsung Semiconductor, Qualcomm… Read More

Design IP Growth Is Fueling 94% of EDA Expansion

Last June, the ESD Alliance (ESDA) has released Q1 2016 results for EDA (CAE, PCB & MCM and IC Physical), Silicon IP (SIP) and Services. Not a surprise for Semiwiki readers since 2013, the SIP category is recognized as the largest with $689 million revenues for the quarter, and four-quarters moving average increasing by 11.6… Read More

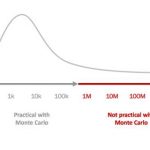

Solido Saves Silicon with Six Sigma Simulation

When pushing the boundaries of power and performance in leading edge memory designs, yield is always an issue. The only way to ensure that memory chips will yield is through aggressive simulation, especially at process corners to predict the effects of variation. In a recent video posted on the Solido website, John Barth of Invecas… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era