Periodically, Mentor commissions a user/usage survey on Functional Verification, conducted by the Wilson Research Group, then they publish the results to all of us, an act of industry good-citizenship for which I think we owe them a round of thanks. Harry Foster at Mentor is breaking down the report into a series of 15 blogs. He’s… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreTSMC 16nm, 10nm, 7nm, and 5nm Update!

Word on the street is that TSMC is on schedule with 16FFC, 10nm and 7nm, which is a very big deal for the fabless semiconductor ecosystem. As Scotten Jones has illustrated in the graphic below, for the first time in the history of the semiconductor industry a pure-play foundry (TSMC) will have the process lead over Intel. And this is… Read More

Apple, Google Go Home

For some marketers the operative mantra is go big or go home. It looks like Apple and Google are both taking a harder look at the automotive industry and have decided to go home.

The media is rife with reports of Apple hemorrhaging automotive engineers while senior executives on Google’s automated driving team have been skipping… Read More

Zero Tolerance = Vision Zero

Just returning from Sweden where the highway fatality rate is a marvel of modern transportation policy. Long before Sweden adopted a Vision Zero approach to reducing highway fatalities the country set itself apart from most others with a 0.02 blood alcohol limit for drivers. There is no question that this has contributed significantly… Read More

Can it ever be game over in tech?

The opening line of a recent Benedict Evans piece makes a bold statement: “The smartphone platform wars are pretty much over, and Apple and Google won.” Reading that line reminded me of the William Shatner scene in Airplane 2; let’s just shut it down and go home. That’s not the point Evans is making, however, … Read More

Requirements Management and IP Management Working Together

I first heard about requirements management back in 1995 while marketing a graphic HDL entry tool for an EDA vendor, and it sounded like a very useful automation approach, however our team quickly discovered that there were too many different vendors for requirements management, so there could be no simple way to integrate with… Read More

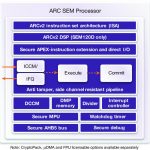

A Powerful Case for the ARC SEM Processor

Building devices for the IoT has become especially challenging thanks to two conflicting requirements. The device has to be small and ultra-low power in most applications but also in many of those applications it has to provide a high-level of security, especially to defend high-value targets like smart metering, payment terminals,… Read More

SoC FPGAs for IoT Edge Computing

One of the reasons for the explosive growth of IoT is that embedded devices with networking capabilities and sensor interfaces are cheap enough to deploy them at a plethora of locations.

However, network bandwidth is limited. Not only that, but also, the latency of the network can be of seconds or minutes. By the time the sensor data… Read More

How Rapidly the Robots Will Rise

“For car buyers, an end to the days of dickering?” reads the headline across the center of the front page of the Washington Post this morning. No, it’s not an article about new tools to make car buying easier. It’s a story about electric vehicle maker, Tesla Motor’s impact on car retailing.

The article… Read More

IOT and Your Utilities Services – Big Savings Coming

The Internet of Things has progressed rapidly in the last decade, providing numerous benefits for consumers, industries, and even government organizations. As a consumer, it can be difficult to break through the noise to see the most important benefits of IoT, especially when the spotlight is often focused on entertainment … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era