Industry 4.0 or, as it is also known the fourth industrial revolution is the trend that is currently coming into play of automating the manufacturing processes and the use of IoT and other technologies to make industrial processes more readily accomplished. It is working hand in hand with things like the internet of things, cloud… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreOptimizing Prototype Debug

In the spectrum of functional verification platforms – software-based simulation, emulation and FPGA-based prototyping – it is generally agreed that while speed shoots up by orders of magnitude (going left to right) ease of debug drops as performance rises and setup time increases rapidly, from close to nothing for simulation… Read More

Final SemiWiki Book Signing at REUSE 2016!

It has been a hectic year for the semiconductor industry so now is a good time to reflect on how we got to where we are today in hopes of better understanding where we are going tomorrow.

Given the importance of semiconductor IP (the $32B ARM acquisition by SoftBank for example) I would strongly suggest attending the REUSE 2016 event… Read More

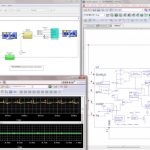

System-level Design for IoT and Automotive

Several years ago a former EDA co-worker went to work for MathWorks, so I started paying a lot more attention to this privately held company that is well known for the MATLAB language and analysis environment. Engineers at MathWorks have created a graphical environment called Simulink for both simulation and model-based design… Read More

#IoT Big Data is worthless!

I have been writing about big data for over three years now. In all that I wrote and many articles that I read, there is an underlying assumption that people naturally accept the huge economic value associated with big data. It turns out that this is a bad assumption. They don’t!

There are many people that see big data as worthless… Read More

Managing the IoT

Now that ARM has introduced its end-to-end IoT, including the mbed Cloud SaaS to handle the cloud end of the IoT, you might wonder what service providers are going to offer on top of this solution. DevicePilot showcased one such solution at ARM TechCon, to manage connected products. These guys especially deserve to be featured because… Read More

CEVA Webinar: Vision Based Autonomous Driving

CEVA Webinar “Challenges of Vision Based Autonomous Driving & Facilitation of An Embedded Neural Network Platform” will be held on November 16[SUP]th[/SUP] and will address one of the hottest topics today in our industry, probably the hottest in the automotive industry as all the players are working hard on autonomous vehicles.… Read More

Executive Interview: Vic Kulkarni of ANSYS

Having known Vic for many years, it is always great to spend time with him and catch up on what is happening inside the semiconductor ecosystem. As Senior Vice President and General Manager, RTL Power Business, at ANSYS in Silicon Valley, Vic spends a lot of time in the field with customers, partners, and at industry events so he has… Read More

What’s Really Going to Limit the IoT?

There’s a lot of hype about the Internet of Things (IoT) as anyone who’s reading anything about these days already knows. There’s wearable tech, there’s healthcare IoT, there’s M2M IoT and a host of other areas of the IoT that are all projected to explode over the next 10 years. Billions and billions of devices are forecast.

Those … Read More

The Fastest Route to V2V

As an occasional rider of the rails in the U.K., I am charmed by the unusual station names. Unfortunately my exposure is limited for the most part to the short run from Euston Station in London to Milton Keynes – the planned city regarded with great disdain by most Brits.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center