This time let’s see if we can stir up some lively debate. Cocotb isn’t new but it is an interesting alternative to mainstream testing methodologies. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford, EE292A) and I continue our series … Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreCan RISC-V Help Recast the DPU Race?

ARM’s Quiet Coup in DPUs

The datacenter is usually framed as a contest between CPUs (x86, ARM, RISC-V) and GPUs (NVIDIA, AMD, custom ASICs). But beneath those high-profile battles, another silent revolution has played out: ARM quietly displaced Intel and AMD in the Data Processing Unit (DPU) market.

DPUs — also called SmartNICs… Read More

Breaking out of the ivory tower: 3D IC thermal analysis for all

Todd Burkholder and Andras Vass-Varnai, Siemens EDA

As semiconductor devices become smaller, more powerful and more densely integrated, thermal management has shifted from an afterthought to a central challenge in modern IC design. In contemporary 3D IC architectures—where multiple chiplets are stacked and closely arrayed—power… Read More

Intel’s Pearl Harbor Moment

There is a lot of talk about where Intel went wrong, the latest is missing AI, but people seem to forget one of the more defining blunders in the history of Intel. In April of 2012 Kirk Skaugen, the new general manager of Intel’s client PC group, moderated a Q&A with Mark Bohr, a 33+ year Intel fellow, and Brad Heaney, the Ivy Bridge… Read More

A Big Step Forward to Limit AI Power Demand

By now everyone knows that AI has become the all-consuming driver in tech and that NVIDIA GPU-based platforms are the dominant enabler of this revolution. Datacenters worldwide are stuffed with such GPUs, serving AI workloads from automatically drafting emails and summarizing meetings to auto-creating software and controlling… Read More

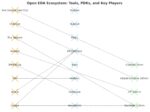

Free and Open Chip Design Tools: Opportunities, Challenges, and Outlook

Designing semiconductor chips has traditionally been costly and controlled by a few major Electronic Design Automation (EDA) vendors—Cadence, Synopsys, and Siemens EDA who dominate with proprietary tools protected by NDAs and restrictive licenses. Fabrication also requires expensive, often export-controlled equipment.… Read More

Chiplets: providing commercially valuable patent protection for modular products

Many products are assembled from components manufactured and distributed separately, and it is important to consider how such products are manufactured when seeking to provide commercially valuable patent protection. This article provides an example in the field of computer chip manufacture.

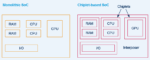

Chiplets

A system-on-a-chip

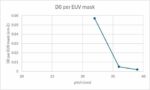

IMEC’s Advanced Node Yield Model Now Addresses EUV Stochastics

It lays the foundation for the Stochastics Resolution Gap

Chris Mack, the CTO of Fractilia, recently wrote of the “Stochastics Resolution Gap,” which is effectively limiting the manufacturability of EUV despite its ability to reach resolution limits approaching 10 nm in the lab [1,2]. As researchers have inevitably found, … Read More

Podcast EP304: PQC Standards One Year On: The Semiconductor Industry’s Next Move

Dan is joined by Ben Packman, Chief Strategy Officer of PQShield. Ben leads global expansion through sales and partner growth across multiple vertical markets, alongside taking a lead role in briefing both government and the supply chain on the quantum threat. He has 30 years of experience in technology, health, media, and telecom,… Read More

Silvaco: Navigating Growth and Transitions in Semiconductor Design

Silvaco Group, Inc., a veteran player in the EDA and the TCAD space, continues to evolve amid the booming semiconductor industry. Founded in 1984 and headquartered in Santa Clara, California, Silvaco specializes in software for semiconductor process and device simulation, analog custom design, and semiconductor intellectual… Read More

ASML High-NA EUV is Not Ready for High-Volume Production