Our smart phone driven semiconductor economy consumes a lot of IP blocks to enable quick product development cycles, often annually updating with new models to choose from. So where do you find all of the best semiconductor IP, verification IP and embedded software? Well, one place is at the 2nd annual REUSE conference, scheduled… Read More

MZ Technologies Launches Advanced Packaging Design Video SeriesIn a significant move aimed at empowering semiconductor…Read More

MZ Technologies Launches Advanced Packaging Design Video SeriesIn a significant move aimed at empowering semiconductor…Read More Superhuman AI for Design Verification, Delivered at ScaleThere is a new breed of EDA emerging.…Read More

Superhuman AI for Design Verification, Delivered at ScaleThere is a new breed of EDA emerging.…Read More The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the DefenseIndustrial control systems (ICS) underpin the world’s most…Read More

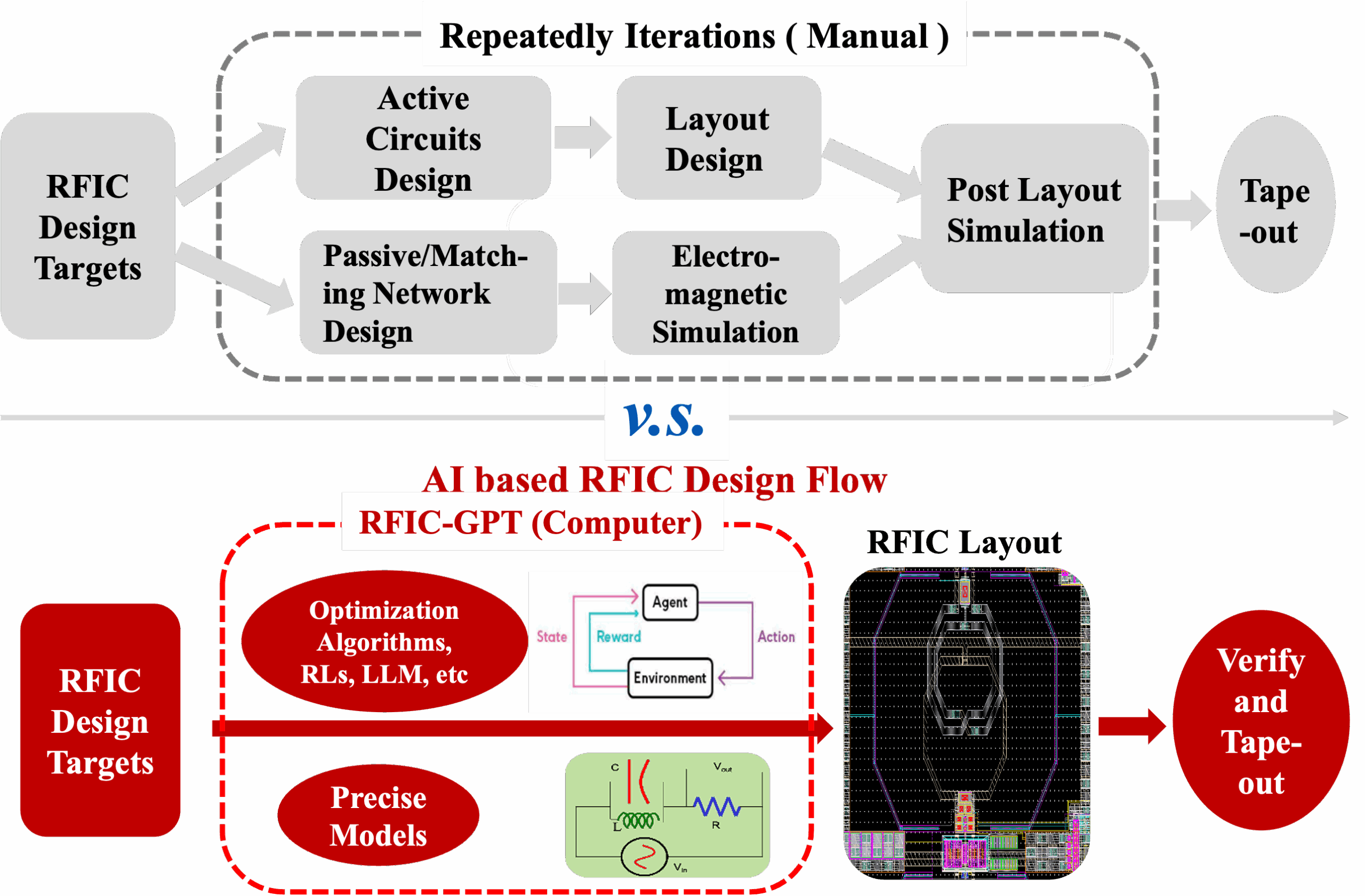

The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the DefenseIndustrial control systems (ICS) underpin the world’s most…Read More Radio Frequency Integrated Circuits (RFICs) Generated by AI Based Design AutomationBy Jason Liu, RFIC-GPT Inc. Radio frequency integrated…Read More

Radio Frequency Integrated Circuits (RFICs) Generated by AI Based Design AutomationBy Jason Liu, RFIC-GPT Inc. Radio frequency integrated…Read MoreWhat are you ready to mobilize for FPGA debug?

There are 3 common misconceptions about debugging FPGA with the real hardware:

[LIST=1]

RISC-V Business

I was at the 7[SUP]th[/SUP] RISC-V Workshop for two days this week. It was hosted by Western Digital at their headquarters in Milpitas. If you have not been following RISC-V, it is an open source Instruction Set Architecture (ISA) for processor design. The initiative started at Berkeley, and has been catching on like wildfire. … Read More

IP-SoC 2017: IP Innovation, Foundries, Low Power and Security

The 20[SUP]th[/SUP] IP-SoC conference will be held in Grenoble, France, on December 6-7, 2017. IP-SoC is not just a marketing fest, it’s the unique IP centric conference, with presentations reflecting the complete IP ecosystem: IP suppliers, foundries, industry trends and applications, with a focus on automotive. It will … Read More

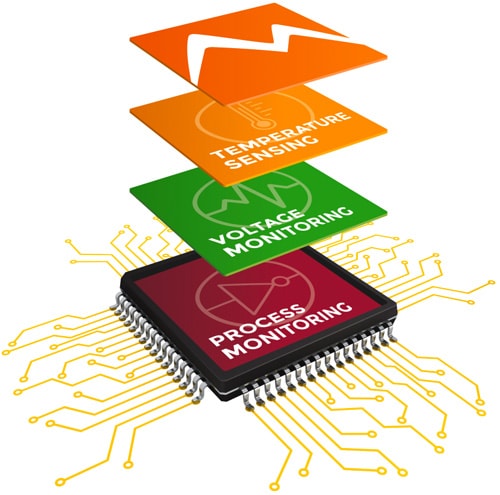

Making Your Next Chip Self-Aware

One holy grail of AI software developers is to create a system that is self-aware, or sentient. A less lofty goal than sentient AI is for chip designers to know how each specific chip responds to Process variations, Voltage levels and Temperature changes. If a design engineer knew exactly which process corner that each chip was fabricated… Read More

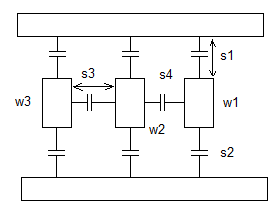

Hierarchy Applied to Semiconductor IP Reuse

When I first started doing IC design back in 1978 we had hierarchical designs, and that was doing a relatively simple 16Kb DRAM chip with only 32,000 transistors using 6um (aka 6,000 nm) design rules. SoC designs today make massive use of hierarchy at all levels of IC design: IC Layout, transistor netlist, gate level netlist, RTL … Read More

A Crossover MCU

Back in the day we had processors which consolidated computing power onto a chip, and out of these sprang (if you’ll excuse the Biblical imagery) microcontrollers (MCUs) in one direction and increasingly complex system-on-chip (SoC) processors in another direction. SoCs are used everywhere today, in smartphones, many IoT … Read More

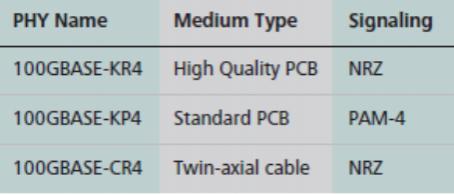

Multi-Channel Multi Rate FEC Engine Webinar with Open Silicon

I will be pleased to moderate on December 7[SUP]th[/SUP] the Open-Silicon webinar addressing the benefits of the multi-channel multi-rate forward error correction (MCMR FEC) IP and the role it plays in high-bandwidth networking applications, especially those where the bit error rate is very high, such as high speed SerDes … Read More

Outsourced Operations: Reduced Risk, Fast Ramp, and Managed Complexity

One of the more interesting semiconductor success stories is Apple and how they transformed from a struggling computer company to a dominant chip maker. We covered this story in quite a bit of detail in our book “Mobile Unleashed” in Chapter 7 “From Cupertino” but the short answer to how they did it is: Outsourced Operations.

Apple’s… Read More

Field-Solver Parasitic Extraction Goes Mainstream

Layout parasitic extraction (LPE) has three primary goals – accuracy, capacity, and throughput. Traditionally, LPE tools have offered two methods for capacitance derivation, with tradeoffs on these goals:… Read More

Quantum Computing Technologies and Challenges