Early last year we talked about state space models, a recent advance over large language modeling with some appealing advantages. In this blog we introduce neurosymbolic methods, another advance in foundation technologies, here applied to automated code generation. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano… Read More

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read More

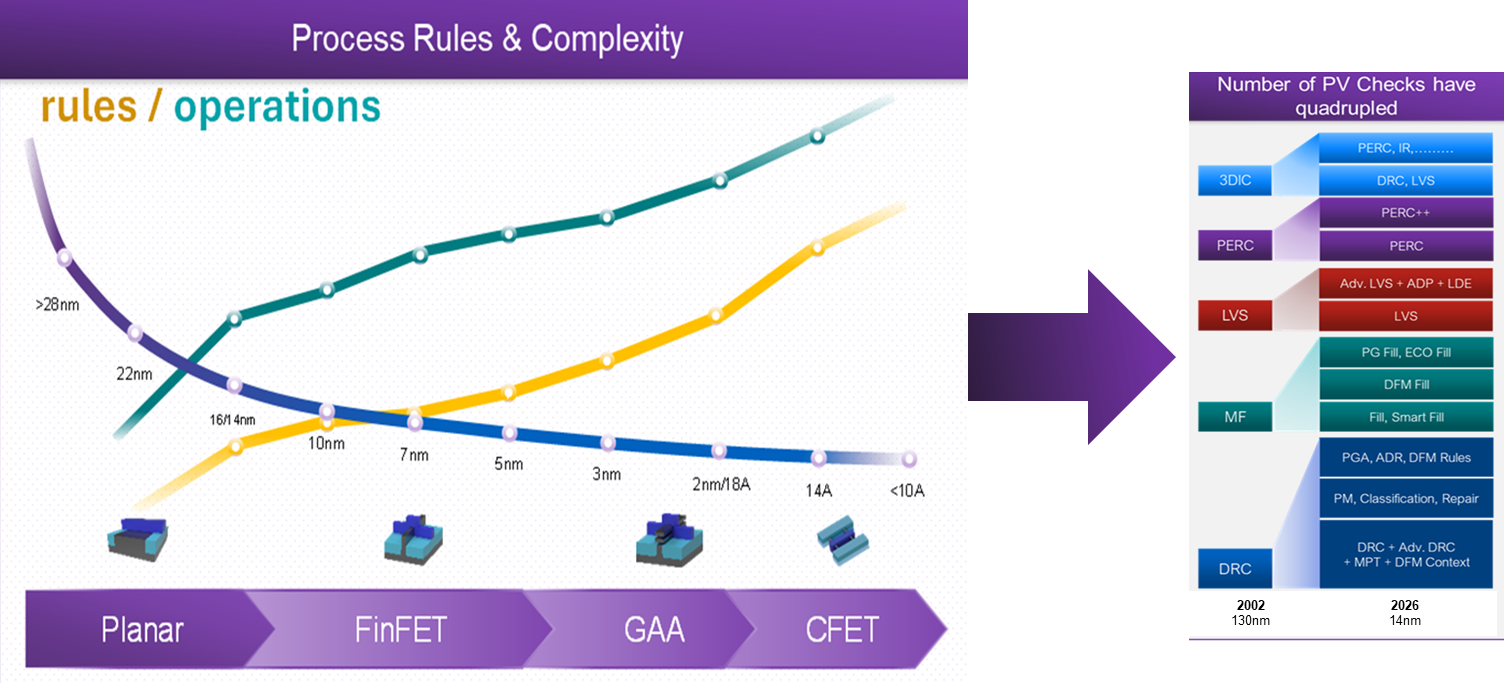

How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read More proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read More

proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read MoreAnalog Bits Steps into the Spotlight at TSMC OIP

The TSMC Open Innovation Platform (OIP) Ecosystem Forum kicked off on September 24 in Santa Clara, CA. This is the event where TSMC recognizes and promotes the vast ecosystem the company has created. After watching this effort grow over the years, I feel that there is nothing the group can’t accomplish thanks to the alignment and… Read More

Synopsys Collaborates with TSMC to Enable Advanced 2D and 3D Design Solutions

Synopsys has deepened its collaboration with TSMC certifying the Ansys portfolio of simulation and analysis tools for TSMC’s cutting-edge manufacturing processes including N3C, N3P, N2P, and A16. This partnership empowers chip designers to perform precise final checks on designs, targeting applications in AI acceleration,… Read More

Via Multipatterning Regardless of Wavelength as High-NA EUV Lithography Becomes Too Stochastic

For the so-called “2nm” node or beyond, the minimum metal pitch is expected to be 20 nm or even less, while at the same time, contacted gate pitch is being pushed to 40 nm [1]. Therefore, we expect via connections that can possibly be as narrow as 10 nm (Figure 1)! For this reason, it is natural to expect High-NA EUV lithography as the go-to

CEO Interview with Jiadi Zhu of CDimension

Jiadi Zhu is the CEO and founder of CDimension, a company rethinking chip design to shape the next generation of computing. Under his leadership, CDimension is creating the next generation of building blocks for chips, starting with materials and scaling up to full systems that can power everything from today’s AI and advanced… Read More

Podcast EP308: How Clockwork Optimizes AI Clusters with Dan Zheng

Daniel is joined by Dan Zheng, VP of Partnerships and Operations at Clockwork. Dan was the General Manager for Product and Partnerships at Urban Engines which was acquired by Google in 2016. He has also held roles at Stanford University and Google.

Dan explores the challenges of operating massive AI hardware infrastructure at … Read More

CEO Interview with Howard Pakosh of TekStart

Howard Pakosh is a serial entrepreneur and angel investor. Mr. Pakosh is also Founder & CEO of the TekStart Group, a Toronto-based boutique incubator focusing on Fractional-C business development support, as well as developing, promoting and licensing technology into markets such as blockchain, Internet-of-Things… Read More

SkyWater Technology Update 2025

SkyWater Technology, a U.S. based pure-play semiconductor foundry, has made significant strides in 2025 reinforcing its position as a leader in domestic semiconductor manufacturing. Headquartered in Bloomington, Minnesota, SkyWater specializes in advanced innovation engineering and high volume manufacturing of differentiated… Read More

TSMC’s Push for Energy-Efficient AI: Innovations in Logic and Packaging

In his keynote at the TSMC OIP Ecosystem Forum Dr. LC Lu, TSMC Senior Fellow and Vice President, Research & Development / Design & Technology Platform, highlighted the exponential rise in power demand driven by AI proliferation. AI is embedding itself everywhere, from hyperscale data centers to edge devices, fueling… Read More

Semiconductor Equipment Spending Healthy

Global spending on semiconductor manufacturing equipment totaled $33.07 billion in the 2nd quarter of 2025, according to SEMI and SEAJ. 2Q 2025 spending was up 23% from 2Q 2024. China had the largest spending at $11.36 billion, 34% of the total. However, China spending in 2Q 2025 was down 7% from 2Q 2024. Taiwan had the second largest… Read More

Is Intel About to Take Flight?