Reason number ONE:The next five DACs will be in San Francisco and this will probably be the last one held in Las Vegas so you absolutely do NOT want to miss it. One of my most memorable DACs was in Las Vegas in 1985. My wife came with me for our second honeymoon and, by definition, it was just that, a honeymoon. This year we will probably spend… Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read MoreESD Alliance CEO Outlook Features Powerhouse Lineup

Just two more weeks before the 2019 CEO Outlook Thursday, May 23, at SEMI. If you haven’t registered yet, do so today. We’re expecting a full house as a result of our powerhouse lineup and networking opportunities.

That lineup includes Ed Sperling, editor in chief of Semiconductor Engineering, who will serve as moderator. Panelists… Read More

Bottom of a Semiconductor Canoe Cycle Shape

Nice numbers despite the cycle bottom

KLA put up EPS of $1.80 versus street of $1.67 on revenues of $1.097B versus street of $1.08B. However guidance was weaker than the street was hoping for with a range of $1.21B to $1.29B in revenues generating between $1.55 and $1.85 in non GAAP EPS. This is compared to current street estimates … Read More

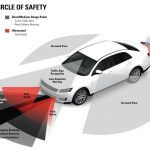

Meeting Automotive IC Design Challenges for Safety using On-Chip Sensors

I’ve been driving cars since 1978 and have even done a few DIY repairs in the garage, so I know how warm the engine compartment, transmission or exhaust system can become which makes automotive IC design rather unique in terms of the high temperature and voltage ranges that an electronic component is subjected to. Our safety… Read More

eSilicon ASICs all in the Google Cloud

Having just completed a cloud evaluation for SemiWiki I can tell you why eSilicon chose Google. Simply put, they are working harder to get cloud business. Google ($4B) is the number five cloud provider behind Microsoft ($21.2B), Amazon ($20.4B), IBM ($10.3B) and Oracle ($6.08B). There is a lot of money in the cloud and a lot more … Read More

Anirudh Keynote at CDNLive 2019

Anirudh Devgan (President of Cadence), gave the third keynote at CDNLive Silicon Valley this year. He has clearly become adept in this role. He has a big, but supportable vision for Cadence across markets and technologies and he’s become a master of the annual tech reveals that I usually associate with keynotes.

Anirudh opened … Read More

When Artificial Intelligence Becomes Emotionally Intelligent

“AI is the biggest risk we face as a civilization.” Words from the visionary Tesla CEO, Elon Musk. After each iteration of innovation, artificial intelligence edges closer to replicating the human brain; people fear that AI would soon steal their jobs, which has already started happening in some parts of the world. Yet, humans … Read More

Design IP in 2018: Synopsys and Cadence Increase Market Share…

…but ARM, Imagination, MIPS or Ceva have declined and lose market share. Semiconductor design IP market is still doing good in 2018, with 6% growth year over year. It’s half the growth rate seen in 2017, 2016 and 2015 and the growth decline is imputable to bad results from ARM, the market leader, but also from Imagination (#4), MIPS… Read More

Blockchain and AI A Perfect Match?

Blockchain and Artificial Intelligence are two of the hottest technology trends right now. Even though the two technologies have highly different developing parties and applications, researchers have been discussing and exploring their combination [6].

PwC predicts that by 2030 AI will add up to $15.7 trillion to the world… Read More

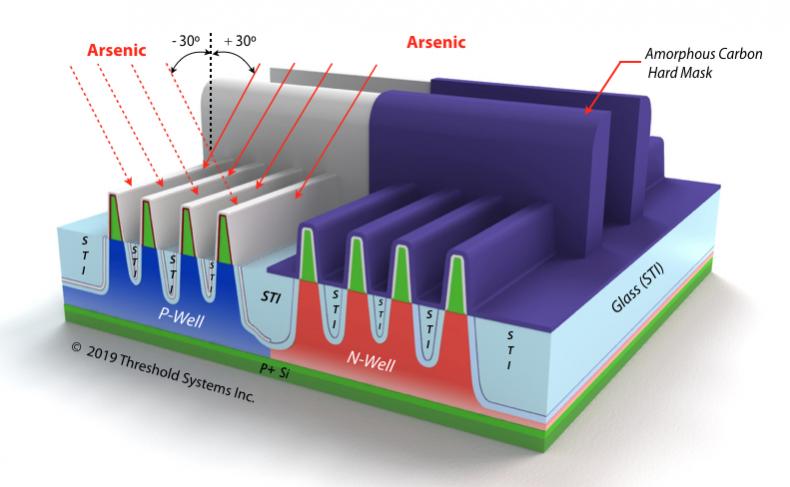

The Evolution of the Extension Implant Part III

The problem of traditional FinFET Extension Implant doping concerns the awkward 3-dimensional structure of the fin. Because the Extension Implant defines the conductive electrical pathway between the Source/Drains and the undoped channel portion of the fin, it is essential that the fin be uniformly doped all three of its surfaces… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry