In this second article about China’s role in the global semiconductor industry I analyse the impact of the Chinese government’s Big Fund and compare Chinese investments in semiconductor R&D with those in other countries. In my previous article, I looked at the possible effects of a US-China decoupling in the… Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

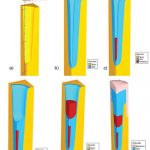

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More3D TCAD Simulation for Power Devices

My first IC design back in 1978 was a DRAM and it ran on 12V, 5V and -5V, but then my second DRAM was using only a 5V supply. Today we see SOCs running under a 1V supply voltage, but there is a totally different market for power devices that are at the other end of the voltage spectrum and they handle switching ranges from 12V – 250V. … Read More

Chapter 8 – Value Through Differentiation in Semiconductor Businesses

Gross Profit Margin Percent Provides a Measure of Product Value

The difference between what customers will pay for a physical product and what it costs to make or acquire it is a good measure of differentiation. This difference divided by the revenue is the gross profit margin percent or GPM%. Once a product has an established market… Read More

GloFo & TSMC lawsuit- A Surrogate Trade War- Pushing TSMC into China’s open arms?

Surrogate Wars

Is GloFo using the trade war as an excuse?

Does TSMC get lumped in with China on trade?

Does this alienate TSMC into China’s embrace?

Much like Vietnam and Korea before it, there have been a number of “surrogate” wars between the US and China as well as many other wars between the US and Russia using… Read More

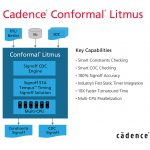

Lint for Implementation

When I was at Atrenta, we took advantage of opportunities to expand our static tool (aka linting) first to clock domain crossing (CDC) analysis and DFT compatibility and later to static analysis of timing constraints, all of which have importance in implementation. CDC is commonly thought of as an RTL-centric analysis, however,… Read More

Webinar: VLSI Design Methodology Development (new text)

Daniel Nenni was gracious enough to encourage me to conduct a brief webinar describing a new reference text, recently published by Prentice-Hall, part of the Semiwiki Webinar Series.

VLSI DESIGN Methodology Development Webiner Replay

Background

I was motivated to write the text to provide college students with a broad background… Read More

IEDM 2019 to Highlight Innovative Devices for an Era of Connected Intelligence

The IEEE International Electron Devices Meeting is in my opinion the leading technology conference to understand the current state-of-the-art in semiconductor process technology. Held each year in early December in San Francisco it is a must attend conference for anyone following technology development. The following is… Read More

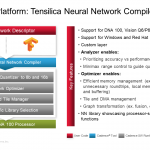

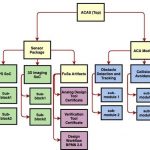

Tensilica DNA 100 Brings the AI Inference Solution for Level 2 ADAS ECUs and Level 4 Autonomous Driving

I recently wrote about Tensilica’s HiFi DSPs which played a significant role at Cadence’s Automotive Design Summit which was held on the Cadence San Jose campus at the end of July. That article focused on infotainment while briefly touching on Advanced Driver-Assistance Systems (ADAS). ADAS is NOT synonymous with autopilot.… Read More

Build More and Better Tests Faster

Breker has been in the system test synthesis game for 12 years, starting long before there was a PSS standard. Which means they probably have this figured out better than most, quite simply because they’ve seen it all and done it all. Breker is heavily involved in and aligned with the standard of course but it shouldn’t be surprising… Read More

Achieving Functional Safety through a Certified Flow

Functional safety (FuSa) is a big deal, especially when driving a car. My beloved 1998 Acura RL recently exhibited a strange behavior at 239K miles, after making a turn the steering wheel would stay tilted in the direction of the last turn instead of straightening out. The auto mechanic pinpointed the failure to the ball joints, … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry