Step into the future of semiconductor design management with IPLM: Future Forward, a product-led webinar showcasing the latest developments in Perforce IPLM. This focused session is designed to show how modern teams can tackle growing design complexity while still accelerating innovation.

Hosted by IPLM… Read More

Agentic AI is often presented as a revolutionary shift in semiconductor manufacturing, driven by large language models and generative AI. However, this framing overlooks an important reality: today’s advances are built on decades of prior work. As Jonathan Holt of PDF Solutions emphasizes in his recent keynote at the APCM 2026… Read More

The semiconductor industry is entering a post-Moore’s Law era in which scaling transistor density alone is no longer sufficient to sustain historical performance growth. As discussed in the panel Beyond Moore’s Law: The Future of Semiconductor Manufacturing, the industry is increasingly dependent on advanced manufacturing… Read More

Matt Crowley is Chief Executive Officer of Scintil Photonics. A physicist by training, Matt built his career transitioning advanced semiconductor technologies from development to volume manufacturing. Before Scintil, he led MEMS technology company Vesper Technologies to high-volume production and through its acquisition… Read More

Daniel is joined by Nir Sever, Senior Director of Business Development at proteanTecs. Nir has over 30 years of experience in advanced VLSI engineering. Before joining proteanTecs, he served for 10 years as the COO of Tehuti Networks, a pioneer in high-speed networking semiconductors. Prior to that, he served for 9 years as Senior… Read More

In the functional verification space, Breker Verification Systems stands out for its vast and long-standing understanding and ability to solve many of the seemingly intractable complexity challenges, especially in the system space.

I recently talked with Dave Kelf, Breker’s CEO, who has plenty of good news to share about Breker’s… Read More

At the recent RISC-V Now by Andes conference, Aion Silicon’s presentation made one thing clear: RISC-V is no longer an emerging alternative but rather rapidly becoming foundational to modern silicon design. This conviction is not theoretical says Oliver Jones, CEO of Aion Silicon, who gave the talk. It is grounded in Aion Silicon’s… Read More

This interview presents the first steps of Robert Simpson (R.S.), a Maths graduate who found an unexpected, but natural home in Formal Verification (FV) at Axiomise. Drawn by a desire to apply rigorous logic to real-world problems, he shares how abstract mathematical thinking translates into ensuring hardware correctness … Read More

Hardware emulation arose as a necessity out of the needs of the eighties. By the mid-1980s, semiconductor designs had outgrown the practical limits of gate-level simulation. Gate-level simulation delivered accuracy, but at glacial pace; silicon prototypes performed at real-speed but arrived far too late. The industry needed… Read More

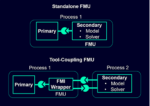

Co-simulation, two or more simulations running concurrently in some manner, is not a new idea. I have written before about multiphysics systems able to model thermal, stress, CFD and other factors simultaneously. I just read a white paper from Siemens based on a different method, using an open standard called the Functional Mockup… Read More

ASML High-NA EUV is Not Ready for High-Volume Production