You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

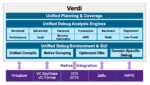

Want fast debug? Synopsys recently hosted a Webinar to show off the latest and greatest improvements to Verdi® in performance, memory demand and multi-tasking, among other areas.

Performance improvements

Taruna Reddy (PMM) and Allen Hsieh (Staff apps) presented features of the latest version, released in March – Taruna started… Read More

Turkey may be the first customer for the Kargu series of weaponized suicide drones specifically developed for military use. These semi-autonomous devices have been in development since 2017 and will eventually be upgraded to operate collectively as an autonomous swarm to conduct mass synchronized attacks.

This situation… Read More

Summary

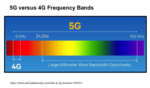

A recent process enhancement in advanced nodes is to support the fabrication of contacts directly on the active gate area of a device. At the recent VLSI 2020 Symposium, the critical advantages of this capability were highlighted, specifically in the context of the behavior of RF CMOS devices needed for 5G designs.

Introduction… Read More

Having spent the last 30 years in semiconductor manufacturing, eight years of this living and working in Asia, it is both exciting and unsettling to see renewed political interest in the revitalization of this industry in the United States. Gone are the days of ‘It doesn’t make any difference whether a country makes computer chips… Read More

I don’t look at the RTL power estimation topic too often these days, so I was interested to see that ANSYS still has a very strong position in this area. Qualcomm is using PowerArtist on one of the most demanding modern applications – mobile GPU power gaming. Mobile gaming heavily loads the GPU, so any optimization in that area will … Read More

In this interview we talk with Sam Mahalingam, chief technology officer at Altair, about gaining a competitive edge with software that’s built to handle high-throughput workloads like chip design and electronic design automation (EDA). Altair is a global technology company providing solutions in product development, high-performance… Read More

Summary

The growing significance of ultra-short reach (USR) interfaces on 2.5D packaging technology has led to a variety of electrical definitions and circuit implementations. TSMC recently presented the approach adopted by their IP development team, for a parallel-bus, clock-forwarded USR interface to optimize power/performance/area… Read More

Intel comes late to the game but will be delivering an embedded defense for Return Oriented Programming (ROP) types of cyber hacks. I first blogged about this back in Sept of 2016. Yes, almost four years have passed and I had hoped it would see the light of day much earlier.

The feature, to debut in the Tiger Lake microarchitecture… Read More

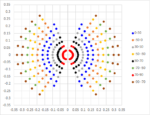

The stochastic nature of imaging has received a great deal of attention in the area of EUV lithography. The density of EUV photons reaching the wafer is low enough [1] that the natural variation in the number of photons arriving at a given location can give rise to a relatively large standard deviation.

In recent studies [2,3], it … Read More

Let me introduce John O’Donnell, CEO of yieldHUB. After earning a degree in microelectronics John spent 18 years at Analog Devices before founding yieldHUB in 2005. If anybody knows yield it is Analog Devices having shipped billions upon billions of chips, absolutely.

SemiWiki will be digging deeper into the technology… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center