The revolutionary Intel 8086 microprocessor was introduced 42 years ago this month so I’ve been studying its die.1 I came across two 8086 dies with different sizes, which reveal details of how a die shrink works. The concept of a die shrink is that as technology improved, a manufacturer could shrink the silicon die, reducing… Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreHow About a Faster Fast SPICE? Much Faster!

When Analog FastSPICE was first introduced in 2006 it changed the landscape for high performance SPICE simulation. During the last 14 years it has been used widely to verify advanced nanometer designs. Of course, since then the most advanced designs have progressed significantly, making verification even more difficult. Just… Read More

Accelerating High-Performance Computing SoC Designs with Synopsys IP

Semiconductor IP is one of the most talked about topics on SemiWiki. Always has been, always will be. Synopsys is also one of the most talked about topics on SemiWiki and IP is a very big part of that, absolutely.

After reading Eric Esteve’s latest IP Report I Googled around and found some interesting things. First, I found a Brief History… Read More

PLDA – Delivering Quality IP with a Solid Verification Process and an Extensive Ecosystem

For those who design advanced and complex SoCs, the term “off-the-shelf IP” can be elusive. While this approach works for a wide range of IP titles, the pressure for maximum performance or minimum power can lead to custom-tailoring requirements for the IP.

PLDA has seen these requirements for the class of complex, high-performance… Read More

Quantifying the Benefits of AI in Edge Computing

Many of us are now somewhat fluent in IoT-speak, though at times I have to wonder if I’m really up on the latest terminology. Between edge and extreme edge, fog and cloud, not to mention emerging hierarchies in radio access networks – how this all plays out is going to be an interesting game to watch. Ron Lowman, DesignWare IP Product… Read More

Cadence Defines a New Signoff Paradigm with Tempus PI

Semiconductor technology advances have a way of rewriting the rule book. As process geometries shrink, subtle effects graduate to mainstream problems. Performance curves can become inverted. And no matter what else occurs, low power demands are constantly reducing voltage and design margins along with it. Sometimes these… Read More

Perforce Software Acquires Methodics!

This has got to be one of the most interesting and disruptive EDA acquisitions I have seen in some time. Another one that comes to mind is Siemens acquiring Mentor Graphics. We have been covering EDA PLM companies since the start of SemiWiki and have worked with most of them. If I had to keep score I would say it’s about even but … Read More

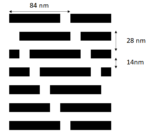

Application-Specific Lithography: a 28 nm Pitch DRAM Active Area

In the recent DRAM jargon, “1X”, “1Y”, “1Z”, etc. have been used to express all the sub-20 nm process generations. It is almost possible now to match them to real numbers which are roughly the half-pitch of the DRAM active area, such as 1X=18, 1Y ~ 17, etc. At this rate, 14 nm is somewhere around

CEO Interview: Anupam Bakshi of Agnisys

Although much of the EDA industry has consolidated into the “Big 3” players, there are still plenty of smaller vendors in the market. In the earlier days of EDA, it seemed that most startups existed only until they failed or did well enough to be acquired. The industry has changed; there are now a number of notable companies that have… Read More

ASML More Covid Concerns and Impact

- Covid related Revenue Rec causes rev/EPS miss

- Sharp order drop reflects H2 industry uncertainty

- EUV remains solid- Memory/Logic mix is better

Results were in line after correcting Covid Caused Revenue Rec issue-

ASML reported revenues of Euro3.3B and EPS of Euro1.79 as revenues from two EUV systems was not recognized, due to … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center