At advanced nodes, the clock is no longer just another signal. It is the most critical and sensitive electrical network on the chip, and the difference between meeting performance targets and missing the tape-out often comes down to a few picoseconds, buried deep inside the clock distribution network. Yet many design teams still… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreCEO Interview with Haber Ma of ADCERAX

Haber Ma is the CEO of ADCERAX and leads the company’s global strategy in advanced ceramic materials for semiconductor and high-performance industrial applications. With a background in engineering, precision manufacturing, and international supply chain development, he has overseen ADCERAX’s transition from a traditional… Read More

WEBINAR: Defacto’s SoC Compiler AI: Democratizing SoC Design with Human Language

Modern chip design has reached unprecedented levels of complexity. Today’s System-on-Chip (SoC) designs integrate multiple processors, complex memory hierarchies, sophisticated interconnects, and much more. All requiring orchestration using complex EDA tool flows. Months are routinely lost to configuration… Read More

An Assistant to Ease Your Transition to PSS

At times it has seemed like any development in EDA had to build a GenAI app that would catch the attention of Wall Street. Now I see more attention to GenAI being used for less glamorous but eminently more practical advances. This recent white paper from Siemens on how to help verification engineers get up to speed faster with PSS is … Read More

Accelerating NPI with Deep Data: From First Silicon to Volume

For decades, semiconductor teams have relied on traditional methods such as corner-based analysis, surrogate monitors, and population-level statistical screening for post-silicon validation. These methods served well when variability was modest, and timing paths behaved predictably. However, today’s advanced nodes… Read More

We Need to Turn Specs into Oracles for Agentic Verification

The natural language understanding now possible in LLMs has raised interest in using specs as a direct reference for test generation, to eliminate need for intermediate and fallible human translation. Sadly, specs today are not an infallible source of truth for multiple reasons. I am grateful to Shelly Henry (CEO of MooresLab)… Read More

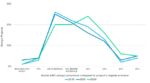

Accelerating SRAM Design Cycles: MediaTek’s Adoption of Siemens EDA’s Additive AI Technology at TSMC OIP 2025

In the competitive vertical of mobile System-on-Chip development, SRAM plays a pivotal role, occupying nearly 40% of chip area and directly impacting yield and performance. The presentation “Accelerating SRAM Design Cycles With Additive AI Technology,” co-delivered by Mohamed Atoua of Siemens EDA and Deepesh… Read More

United Micro Technology and Ceva Collaborate for 5G RedCap SoC and Why it Matters

In the ultra competitive automotive technology race the integration of advanced connectivity is no longer a luxury but a necessity. As vehicles transition from isolated machines to intelligent nodes in a vast ecosystem, seamless, reliable communication becomes paramount. On November 11, 2025, Ceva, Inc., a leading licensor… Read More

Transforming Functional Verification through Intelligence

SoC projects are running behind schedule as design and verification complexity has increased dramatically, so just adding more engineers, more tests and more compute aren’t the answer. The time is ripe to consider smarter ways to improve verification efficiency. The added complexity of multiple embedded processors, multiple… Read More

Podcast EP320: The Emerging Field of Quantum Technology and the Upcoming Q2B Event with Peter Olcott

Daniel is joined by Peter Olcott, Deeptech Principal at First Spark Ventures specializing in early-stage investments. His background encompasses over 20 years of experience in electrical engineering, software engineering, algorithm design, combined hardware-software robotic devices, and novel innovations in biomedical… Read More

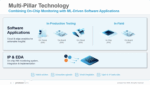

Solving the EDA tool fragmentation crisis