What do genome sequencing, engineering modeling and simulation, and big data analytics have in common? They’re all bandwidth-hungry applications with complex data workloads. High-performance computing (HPC) systems deliver the parallel processing capabilities to generate detailed and valuable insights from these applications.

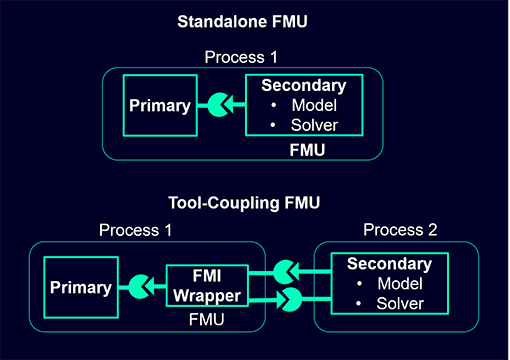

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More

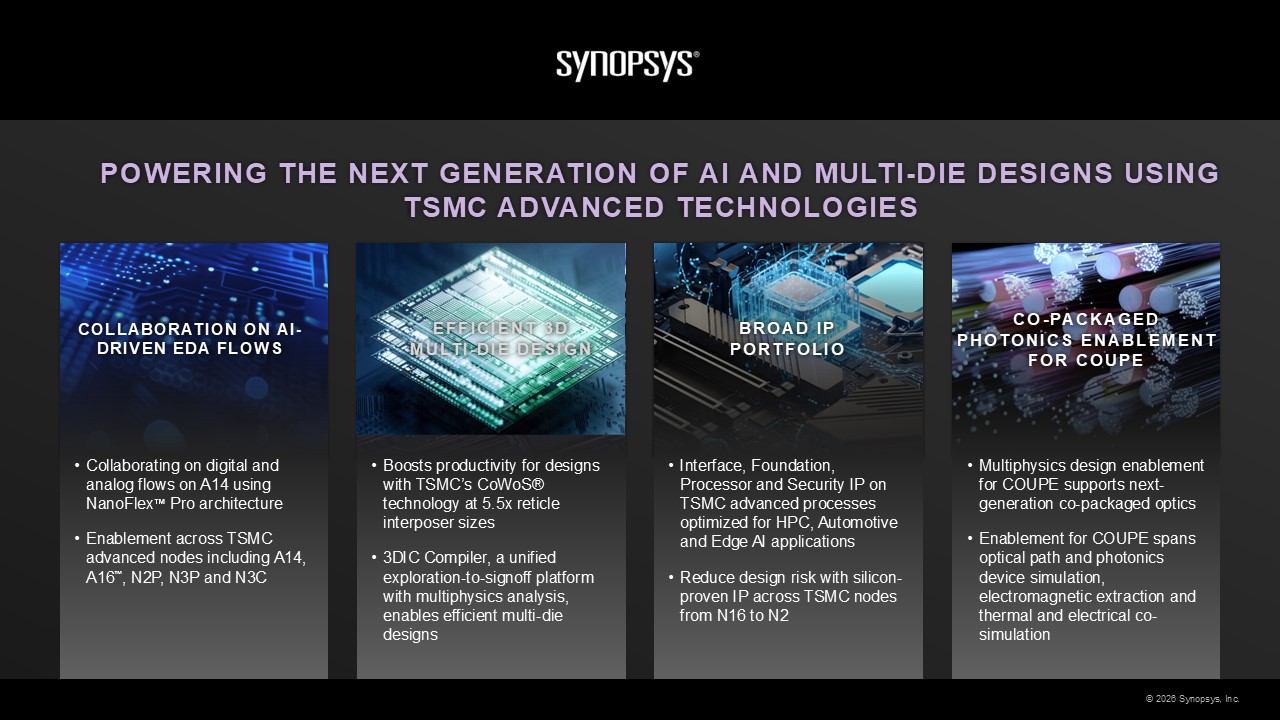

Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

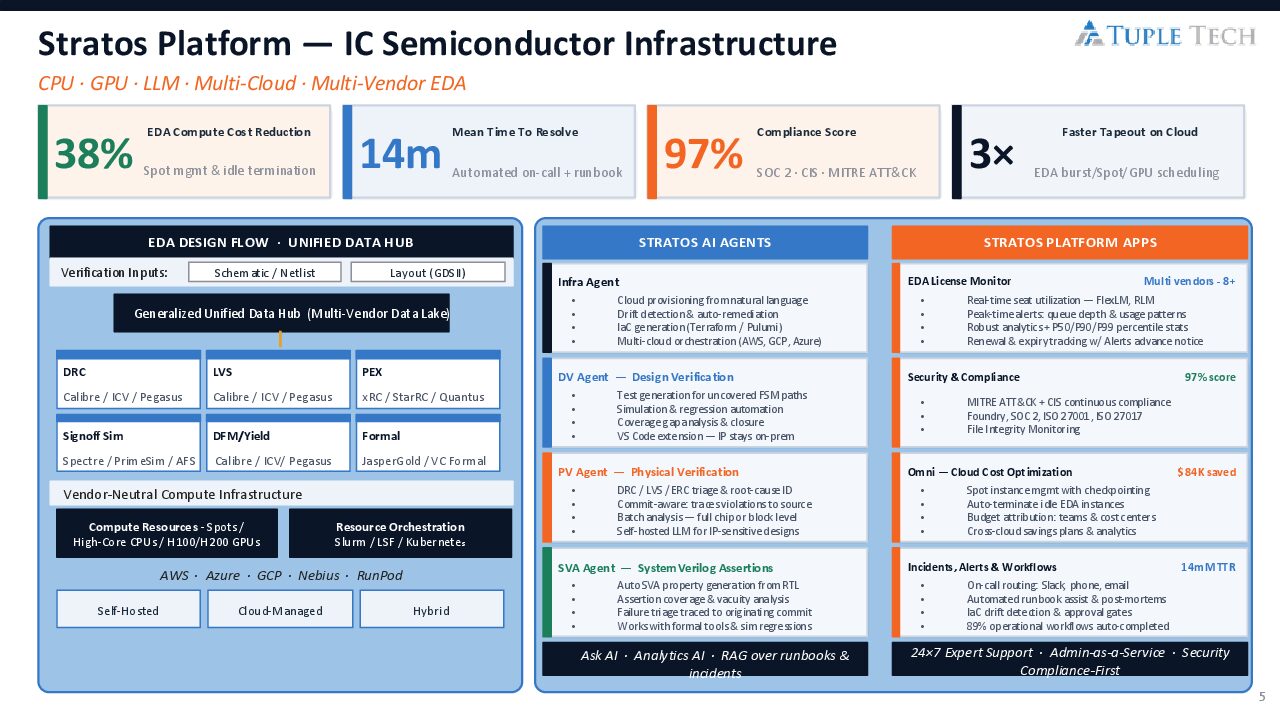

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreeFPGA IP – in Videos

eFPGA has been a hot topic on SemiWiki for the past five years and it is still going strong. eFPGA is more descriptively categorized as embedded programmable logic and reconfigurable computing. Whatever you want to call it, eFPGA is an important piece of the computing puzzle, absolutely.

We recently did a series of videos with Menta… Read More

Meeting the Need for Hardware-Assisted Verification

Editor’s Note: Siemens EDA recently introduced a comprehensive hardware-assisted verification system comprised of hardware, software and system verification that streamlines and optimizes verification cycles while helping reduce verification cost. What follows is an edited version of an interview Verification Expert… Read More

Apple’s Cook Paints Himself into an Autonomous Corner

These days tech journalists and analysts appear confident of one thing. Apple is working on an autonomous car.

There’s a “Garbo Talks” quality to the tea leaf reading around Apple’s autonomous vehicle development efforts. The latest chapter was written with the publication of Kara Swisher’s latest “Sway” podcast episode

Technology Under Your Skin: 3 Challenges of Microchip Implants

As technology continues to get closer to merge with our bodies, from the smart phones in our hands to the smartwatches on our wrists to earbuds. Now, it’s getting under our skin literally with a tiny microchip. A human microchip implant is typically an identifying integrated circuit device or RFID (Radio-Frequency IDentification)… Read More

Podcast EP15: The Birth of Dynamically Reconfigurable Computing

Dan and Mike are joined by Geoff Tate, founding CEO of Flex Logix. Geoff has a storied career in semiconductors that includes over ten years at AMD, ending as senior VP, microprocessors and logic. Following AMD, Geoff was founding CEO of Rambus, growing the company from four people to IPO with a $2 billion market cap.

As co-founder… Read More

CEO Interview: Kush Gulati of Omni Design Technologies

Kush Gulati is the CEO of Omni Design Technologies, a company he co-founded in 2015 to lead a transformation in how high-performance analog IP is developed and integrated into SoCs in advanced process nodes. With a PhD from MIT, he is a renowned expert in data converters, and a serial entrepreneur. His first startup was a detective… Read More

SPIE 2021 – Applied Materials – DRAM Scaling

At the SPIE Advanced Lithography Conference in February 2021, Regina Freed of Applied Materials gave a paper: “Module-Level Material Engineering for Continued DRAM Scaling”. Applied Materials provided me with the presentation and was kind enough to set up an interview for me with Regina Freed.

I also spoke to Regina Freed last… Read More

Cadence Dynamic Duo Upgrade Debuts

Cadence calls their hardware acceleration platforms, Palladium Z2 for fast pre-silicon hardware debug and Protium X2 for fast pre-silicon software validation, their Dynamic Duo. With good reason. Hardware acceleration is now fundamental to managing the complexity of verification and validation for large systems, hardware… Read More

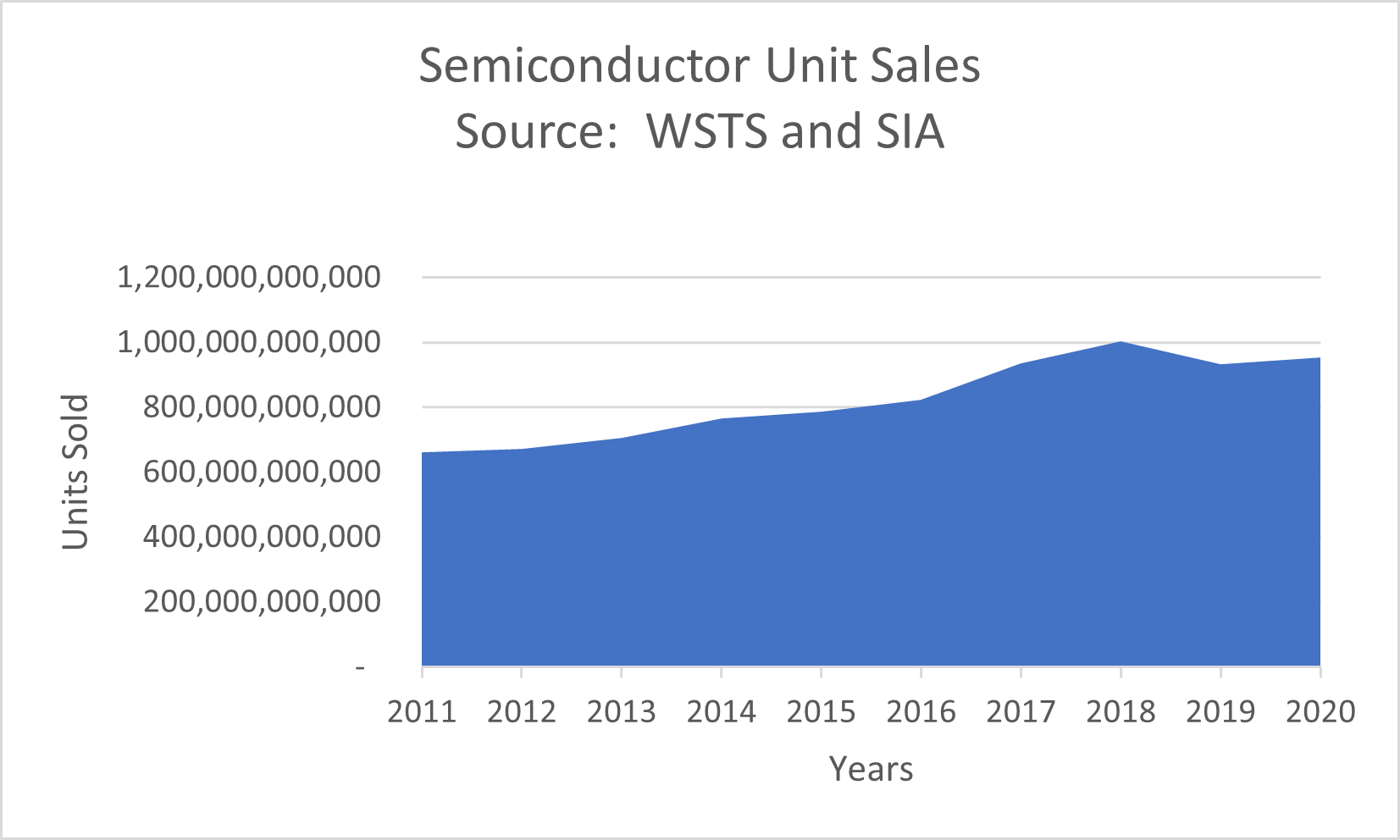

Is E-Waste Declining ? The rest of the story

Recently, there have been a number of articles with titles such as “Study shows residential electronic scrap generation is declining” or “E-scrap generation on the decline, study finds.” or “E-Waste Is Declining, Government Needs To Change Laws To Keep Up – And Get Out Of The Recycling Business.”

As a veteran of … Read More

Siemens U2U 3D IC Design and Verification Panel