In an upcoming Innovation blog we’ll get into how quantum computers are programmed. Here I’d like to look more closely at algorithms beyond Grover and Shor, and what practical applications there might be for quantum computing. I also take a quick look at what analysts are saying about potential market size. Even more than in AI, … Read More

Live Event: Engineering the Future of AI SystemsThe rapid acceleration of artificial intelligence (AI) workloads…Read More

Live Event: Engineering the Future of AI SystemsThe rapid acceleration of artificial intelligence (AI) workloads…Read More proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read More

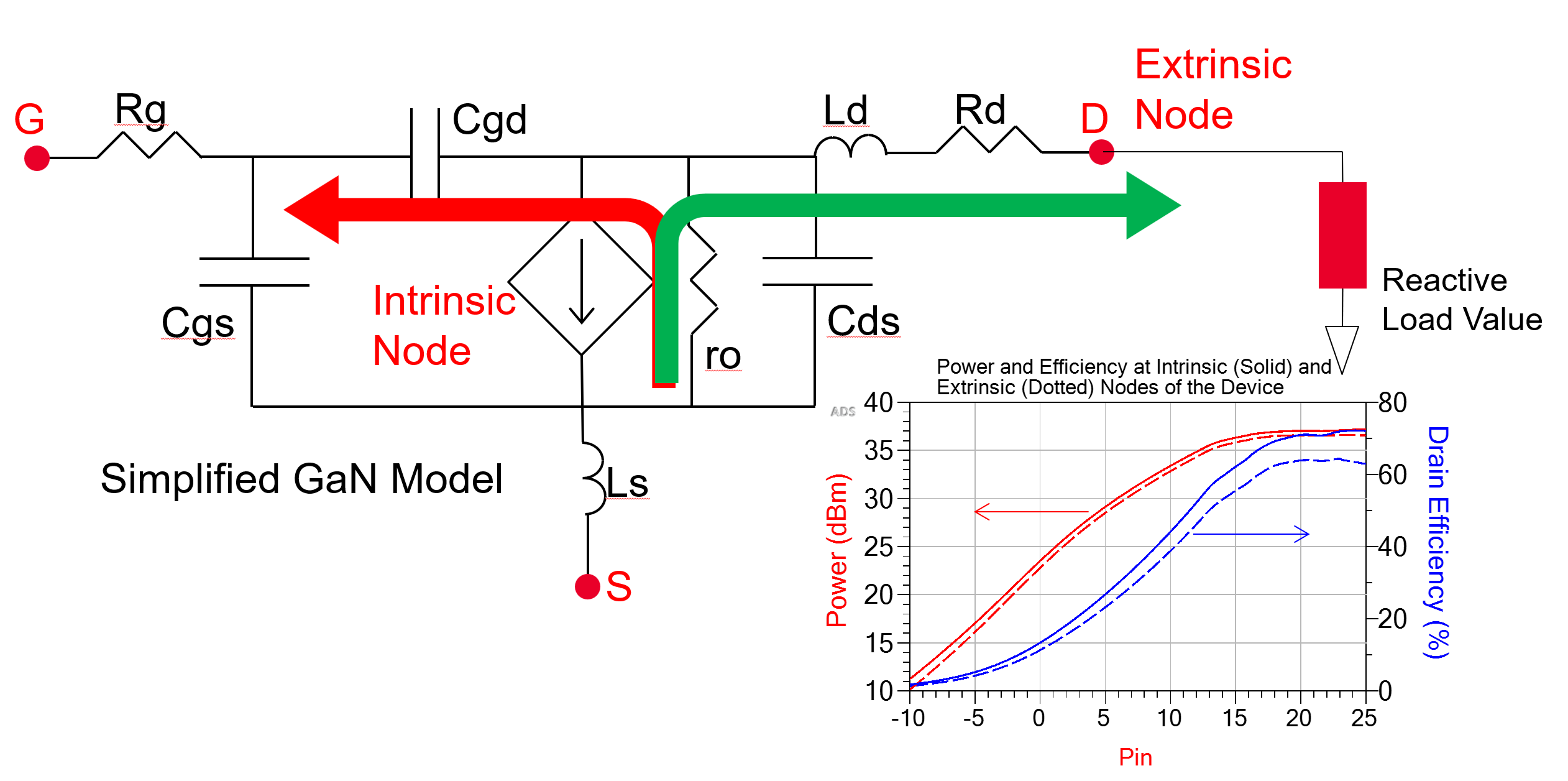

proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read More WEBINAR: Intrinsic Techniques in RF Power Amplifier DesignLoad-pull power amplifier (PA) design techniques determine the…Read More

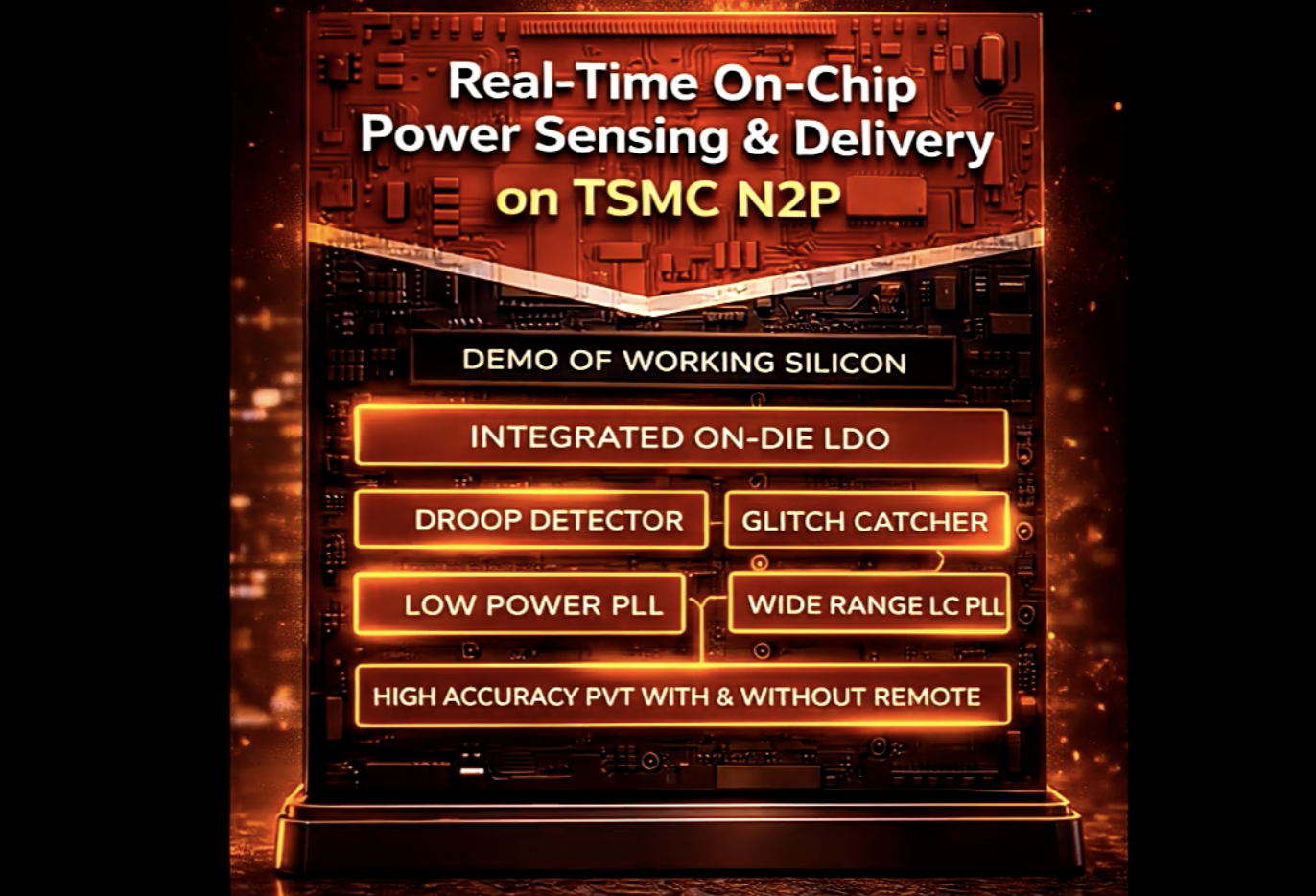

WEBINAR: Intrinsic Techniques in RF Power Amplifier DesignLoad-pull power amplifier (PA) design techniques determine the…Read More Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read Moreimec on the Benefits of ASICs and How to Seize Them

In an era where product differentiation increasingly depends on performance, power efficiency, and form factor, Application-Specific Integrated Circuits (ASICs) have become the ultimate competitive weapon for innovative companies. Unlike off-the-shelf processors, FPGAs, or even ASSPs, a full- or semi-custom ASIC is… Read More

CEO Interview with Eelko Brinkhoff of PhotonDelta

In 25 years of working in economic development, Eric gained a lot of experience and knowledge in the field of Foreign Direct Investments (FDI), internationalisation of SME’s, innovation cooperation and economic development. I have built a strong network in the Netherlands and abroad towards business, government, knowledge… Read More

Podcast EP322: A Wide-Ranging and Colorful Conversation with Mahesh Tirupattur

Daniel is joined by Mahesh Tirupattur, chief executive officer at Analog Bits. Mahesh leads strategic planning to develop and implement Analog Bits’ vision and mission of enabling the silicon digital world with interfacing IP to the analog world. Additionally, Mahesh oversees all aspects of Analog Bits’ operations to ensure… Read More

MZ Technologies Launches Advanced Packaging Design Video Series

In a significant move aimed at empowering semiconductor and systems-design engineers, MZ Technologies has announced the launch of a new video series focused on advanced packaging design. This initiative comes at a time when the semiconductor industry is rapidly shifting toward multi-die, 2.5D/3D integration, heterogeneous… Read More

Superhuman AI for Design Verification, Delivered at Scale

There is a new breed of EDA emerging. Until recently, EDA tools were focused on building better chips, faster and with superior quality of results. Part of that process is verifying and debugging the resultant design. Thanks to ubiquitous AI workloads and multi-chip architectures, the data to be verified and debugged is exploding,… Read More

The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the Defense

Industrial control systems (ICS) underpin the world’s most critical infrastructure: power grids, manufacturing plants, transportation networks, water systems, oil and gas facilities, and chemical processing operations. For decades, these systems relied on isolation, proprietary communication protocols, and hardware… Read More

AI Deployment Trends Outside Electronic Design

In a field as white-hot as AI it can be difficult to separate cheerleading from reality. I am as enthusiastic as others about the potential but not the “AI everywhere in everything” message that some emphasize. So it was interesting to find a survey which looks at the deployment reality outside our narrow domain of electronic and … Read More

CAST’s Breakthrough in Automotive IP: The MSC-CTRL Microsecond Channel Controller

In a significant advancement for automotive electronics, Semiconductor intellectual property provider CAST has unveiled the MSC-CTRL Microsecond Channel Controller IP core. This new core empowers ASIC and FPGA designers with a deterministic, microsecond-precise serial interface for connecting to smart power and sensor… Read More

Radio Frequency Integrated Circuits (RFICs) Generated by AI Based Design Automation

By Jason Liu, RFIC-GPT Inc.

Radio frequency integrated circuits (RFICs) have become increasingly critical in modern electronic systems, driven by the rapid growth of wireless communication technologies (5G/6G), the Internet of Things (IoT), and advanced radar systems. With the desire for lower power consumption, higher… Read More

Is Intel About to Take Flight?