For Tesla, 2021 was an amazing year. A blindspot looms in 2022.

Critics cheered the National Highway Traffic Safety Administration for opening multiple investigations into fatal and near fatal Tesla crashes. Legislators decried the de facto beta testing of Tesla’s Full Self-Driving beta on public roads. And in December,… Read More

Too much demand- A “good” problem-Managing supply & capacity-Intel & Hi NA

–ASML great Q4 results-Demand off charts-Supply constrained

-Dealing with chain issues, putting out fires, expediting

-Looking forward to next gen High NA in 2024/2025

-Intel’s order doesn’t give advantage,… Read More

Daniel Nenni is joined by popular podcast guest Wally Rhines. Dan and Wally explore 2021, some of the expected results and some of the surprises. COVID, supply chains, chip shortages and international trade are just a few of the topics.

Wally and Dan then turn their attention to 2022. What kind of year will it be? What will be the … Read More

There has been a lot of attention in the news recently about AT&T and Verizon rolling out their first implementations of sub-6GHz 5G radio access networks (RAN). Notably, the FAA and airline industries have voiced serious concerns about potential safety issues for aircraft autopilot and landing systems. As a result of these… Read More

Hello! The most important semiconductor company in the world reported earnings last night. It’s been something of a tradition to post Taiwan Semiconductor Company (TSMC) earnings posts not behind my paywall, and I think that I’m going to continue that to kickoff each earnings season.

There are so many threads in the TSMC call that… Read More

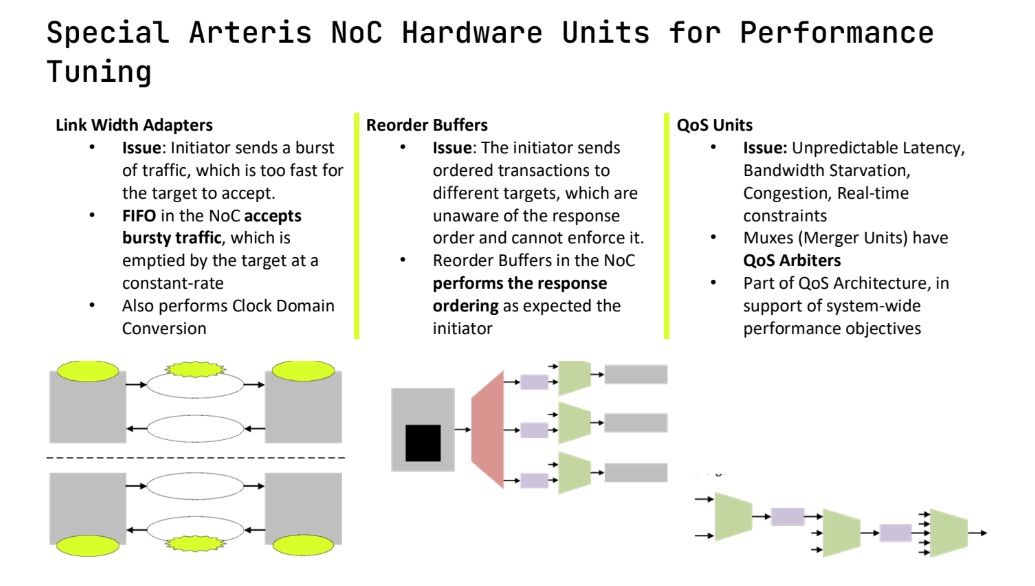

Dan is joined by Charlie Janac, president and CEO of Arteris IP. Charlie’s career spans 20 years in multiple industries, including design automation, semiconductor capital equipment, nanotechnology, industrial polymers, and venture capital.

Charlie discusses the benefits of using network-on-chip, or NoC IP on several… Read More

-Chips for America is better than nothing, but not much

–TSMC $40-44B Capex crushes competition (Intel & Samsung)

-Additional efforts other than handouts are necessary

-Could/should TSMC be “adopted” as a US company?

Competition can’t keep up with $40-$44B of Capex

TSMC’s recent announcement… Read More

Last month, eMemory Technology hosted a webinar titled “eMemory’s Embedded Logic-NVM Solution for AI Chips.” While the purpose was to present their embedded Logic-NVM solution, the webinar nicely sets the stage by highlighting Analog NVM’s value as it relates to neural networks. Of course, the algorithms of neural networks… Read More

Cornami is an interesting company. Their leader is also an interesting person. I’ve interviewed Wally Rhines many times on various topics. All of them have been big hits. Cornami is focused on enabling fully homomorphic encryption (FHE) in a commercially viable and widespread manner. Many say this isn’t possible, but Wally and… Read More

As we established last year, we will use the January issue of this blog to look back at the papers we reviewed last year. We lost Jim Hogan and the benefit of his insight early last year, but we gained a new and also well-known expert in Raúl Camposano (another friend of Jim). Paul (GM, Verification at Cadence), Raúl (Silicon Catalyst,… Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute Blueprint