The burgeoning use of conversational artificial intelligence (CAI) in consumer and business applications places a heavy computational burden on both front-end and back-end systems that provide the natural language processing (NLP). NLP systems rely on deep learning (a subset of machine learning) to automate speech recognition,… Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read MoreCasting Light on OpenLight’s Open Silicon Photonics Platform

For many decades now, modern optical technology has been deployed in networking infrastructure, for long haul and medium haul links to support internet communications. The foundation of this technology is photonics, which is the science of generation, manipulation and detection of light for performing functions otherwise… Read More

Obscuration-Induced Pitch Incompatibilities in High-NA EUV Lithography

The next generation of EUV lithography systems are based on a numerical aperture (NA) of 0.55, a 67% increase from the current value of 0.33. It targets being able to print 16 nm pitch [1]. The High-NA systems are already expected to face complications from four issues: (1) reduced depth-of-focus requires thinner resists, which… Read More

CHIPS for America DOA?

- We think hopes for CHIPS for America is fading fast

- Politics, Jan 6th, guns, inflation, partisanship will likely block it

- Alternative to building US semis is knocking down China chips

- The only political option may be more restrictions on China

Chips for America act seems drowned out by partisan screaming

We have been saying, for… Read More

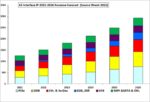

Semiconductors Weakening in 2022

The semiconductor market in 2022 is weakening. Driving factors include rising inflation, the Russian war on Ukraine, COVID-19 related shutdowns in China, and lingering supply chain issues. Four of the top 14 semiconductor companies (Intel, Qualcomm, Nvidia and Texas Instruments) are expecting lower revenues in 2Q 2022 versus… Read More

Podcast EP88: A conversation with Maheen Hamid, one of Silicon Valley’s 100 Most Influential Women

Dan is joined by Maheen Hamid, Chief Operating Officer and Chief Financial Officer at Breker Verification Systems and a recipient of Silicon Valley Business Journal’s 100 most influential women award. Maheen discusses her journey to Silicon Valley and Breker, beginning with her upbringing in Bangladesh. Maheen married… Read More

Stop-For-Top IP Model to Replace One-Stop-Shop by 2025

…and support the creation of successful Chiplet business

The One-Stop-Shop model has allowed IP vendors of the 2000’s to create a successful IP business, mostly driven by consumer application, smartphone or Set-Top-Box. The industry has dramatically changed, and in 2020 is now driven by data-centric application (datacenter,… Read More

Three Key Takeaways from the 2022 TSMC Technical Symposium!

The TSMC Technical Symposium is today so I wanted to give you a brief summary of what was presented. Tom Dillinger will do a more technical review as he has done in the past. I don’t want to steal his thunder but here is what I think are the key takeaways. First a brief history lesson.

The history of TSMC Technology Development with 12 key… Read More

Podcast EP87: How Axiomise Addresses the Verification Challenge

Dan is joined by GD Bansal, COO at Axiomise. Dan explores the Axiomise business model to provide training and consulting services for formal verification with GD. The benefits and challenges of using formal verification on complex designs are discussed, along with the benefits of the Axiomize vendor-neutral approach to … Read More

HLS in a Stanford Edge ML Accelerator Design

I wrote recently about Siemens EDA’s philosophy on designing quality in from the outset, rather than trying to verify it in. The first step is moving up the level of abstraction for design. They mentioned the advantages of HLS in this respect and I refined that to “for DSP-centric applications”. A Stanford group recently presented… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center