The success of modern battery-powered products depends as much on useful operating time between charges as on functionality. FinFET process technologies overtook earlier planar CMOS in part because they significantly reduce leakage power. But they exacerbate dynamic power consumption thanks to increased pin capacitances.… Read More

WEBINAR: Revolutionizing Electrical Verification in IC DesignIn the complex world of IC design, electrical…Read More

WEBINAR: Revolutionizing Electrical Verification in IC DesignIn the complex world of IC design, electrical…Read More Silicon Catalyst on the Road to $1 Trillion IndustryThere were quite a few announcements at the…Read More

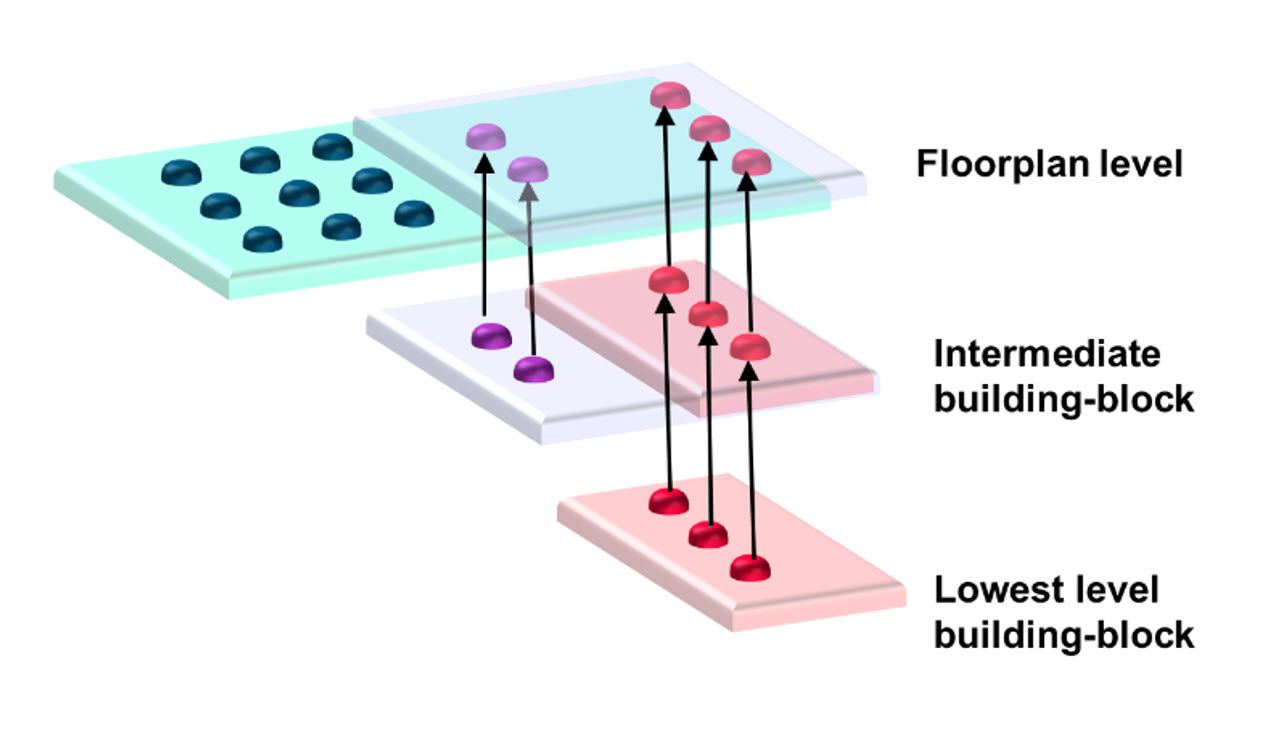

Silicon Catalyst on the Road to $1 Trillion IndustryThere were quite a few announcements at the…Read More Hierarchically defining bump and pin regions overcomes 3D IC complexityBy Todd Burkholder and Per Viklund, Siemens EDA…Read More

Hierarchically defining bump and pin regions overcomes 3D IC complexityBy Todd Burkholder and Per Viklund, Siemens EDA…Read More CDC Verification for Safety-Critical Designs – What You Need to KnowVerification is always a top priority for any…Read More

CDC Verification for Safety-Critical Designs – What You Need to KnowVerification is always a top priority for any…Read More Ceva Unleashes Wi-Fi 7 Pulse: Awakening Instant AI Brains in IoT and Physical RobotsIn the rapidly evolving landscape of connected devices,…Read More

Ceva Unleashes Wi-Fi 7 Pulse: Awakening Instant AI Brains in IoT and Physical RobotsIn the rapidly evolving landscape of connected devices,…Read MoreThe Clash Between 5G and Airline Safety

For 5G to really deliver on its promise of high bandwidth and good coverage, it needs to use an RF band known as C-Band (3.7 to 4.4 GHz). This band is ideal because its frequency is high enough to offer 100MHz wide channels and also low enough that signal attenuation, especially in urban areas, is minimal. In 2020 the FCC auctioned off… Read More

Six Essential Steps For Optimizing EDA Productivity

Altair® Accelerator™ was the focus of a couple of SemiWiki posts last year. The most recent post covers the enterprise-grade job scheduler’s latest updates and an earlier one discussed its patented Rapid Scaling feature. You can refer to these blogs here. While these posts provide insight into how Accelerator can help increase… Read More

Automated Documentation of Space-Borne FPGA Designs

Over the past three years, I’ve spoken frequently with Cristian Amitroaie, CEO and co-founder of AMIQ EDA, to understand how the company is helping engineers cope with the challenges of chip design and verification. With their broad customer base and many years of experience in the EDA business, the folks at AMIQ really seem to … Read More

Intel 2022 Investor Meeting

Last Thursday Intel held their investors meeting, in this write up I wanted to focus on my areas of coverage/expertise, process technology and manufacturing.

Technology Development presented by Ann Kelleher

Last year Intel presented their Intel Accelerated plan and, in this meeting, we got a review of where Intel stands on that… Read More

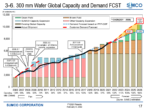

Semiconductor Earnings Roundup

ON, ACLS, RMBS, AOSL, CAMT, ICHR, ONTO, SUMCO, and more!

SUMCO was the best call I read this quarter. There were many great bits of information but I want to start with the stat that really shocked me.

First of all, with regard to the LTAs out to 2026 and whether we did make progress in the last 3 months, that is correct. In the last 3 months,

AMAT – Supply Constraints continue & Backlog Builds- Almost sold out for 2022

-Production constraints push backlog up $1.3B to $8B

-Looks like $100B in WFE 2022 VS $80B in 2021

-Almost sold out for 2022- Could lead to continued growth 2023

-Insp/metrology up 68% Y/Y- Expect steady growth in 2022

Can’t keep up with demand….

Revenue came in at $6.27B and NonGAAP EPS of $1.89. A very slight beat of … Read More

Podcast EP63: The growing importance of interconnect architecture

Dan and Mike are joined by Matt Burns, technical marketing manager at Samtec. Matt focuses on why interconnect architecture has become so important for state-of-the-art system designs. The markets that are driving these requirements, along with the challenges and how to address them are provided.

The discussion concludes… Read More

CEO Interview: John Mortensen of Comcores

John Mortensen is the CEO & CCO of Comcores. He has been with Comcores since 2019, and has been leading the commercial function since 2020 and was appointed CEO in early 2021. John is focused on creating the best possible customer experience when you do business with Comcores. An experience where you, as a customer, sense how … Read More

Tower Semi Buyout Tips Intel’s Hand

The rationale behind the Tower Semi acquisition and things to watch out for at Intel’s investor day.

Intel bids for Tower Semi

First I have to quote myself because Tower was an error of omission. In November in a piece that was likely too long for its own good, I mentioned that trailing edge fabs are in a huge position of strength… Read More

An Insight into Building Quantum Computers