Ever wonder why coherent networks are needed beyond server design? The value of cache coherence in a multi-core or many-core server is now well understood. Software developers want to write multi-threaded programs for such systems and expect well-defined behavior when accessing common memory locations. They reasonably expect… Read More

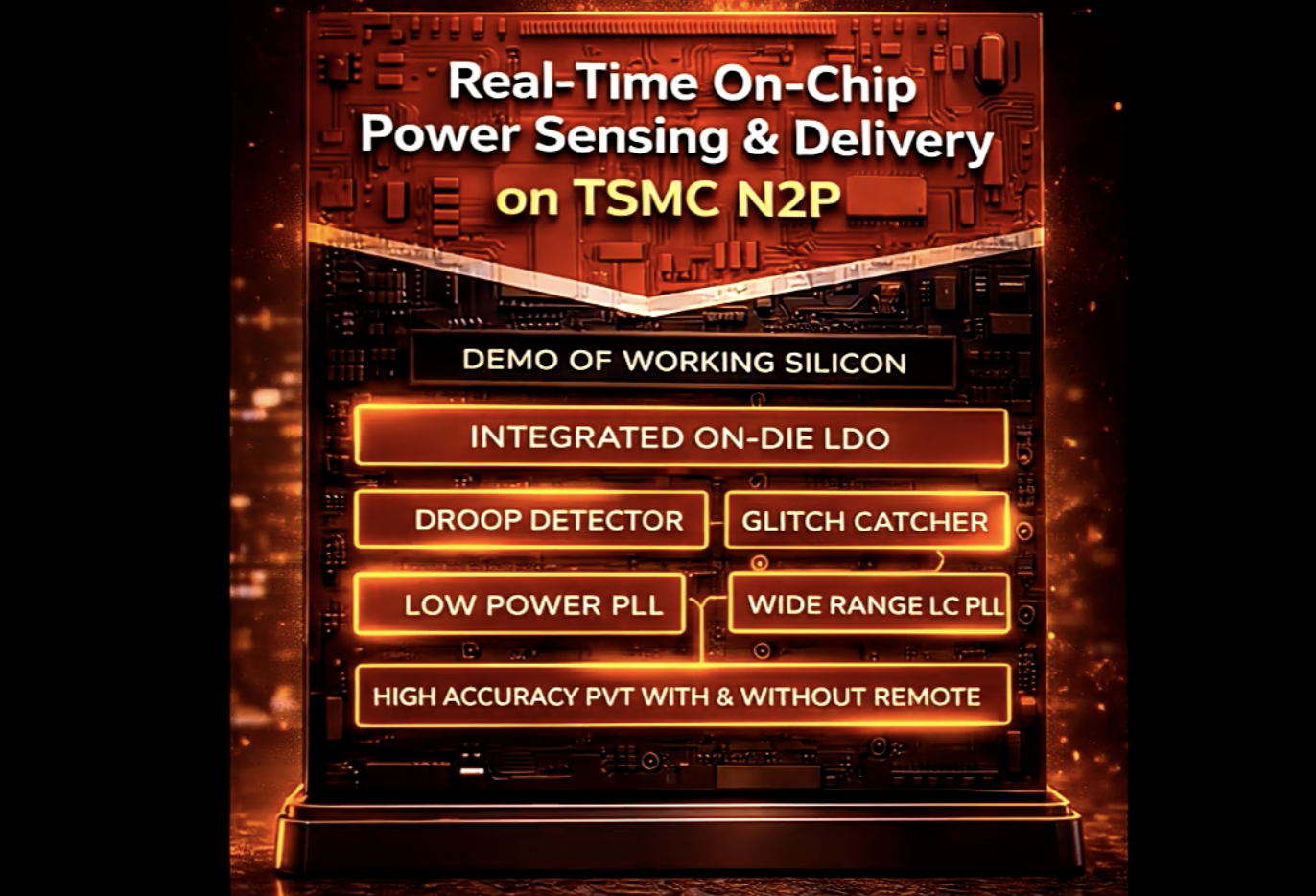

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More

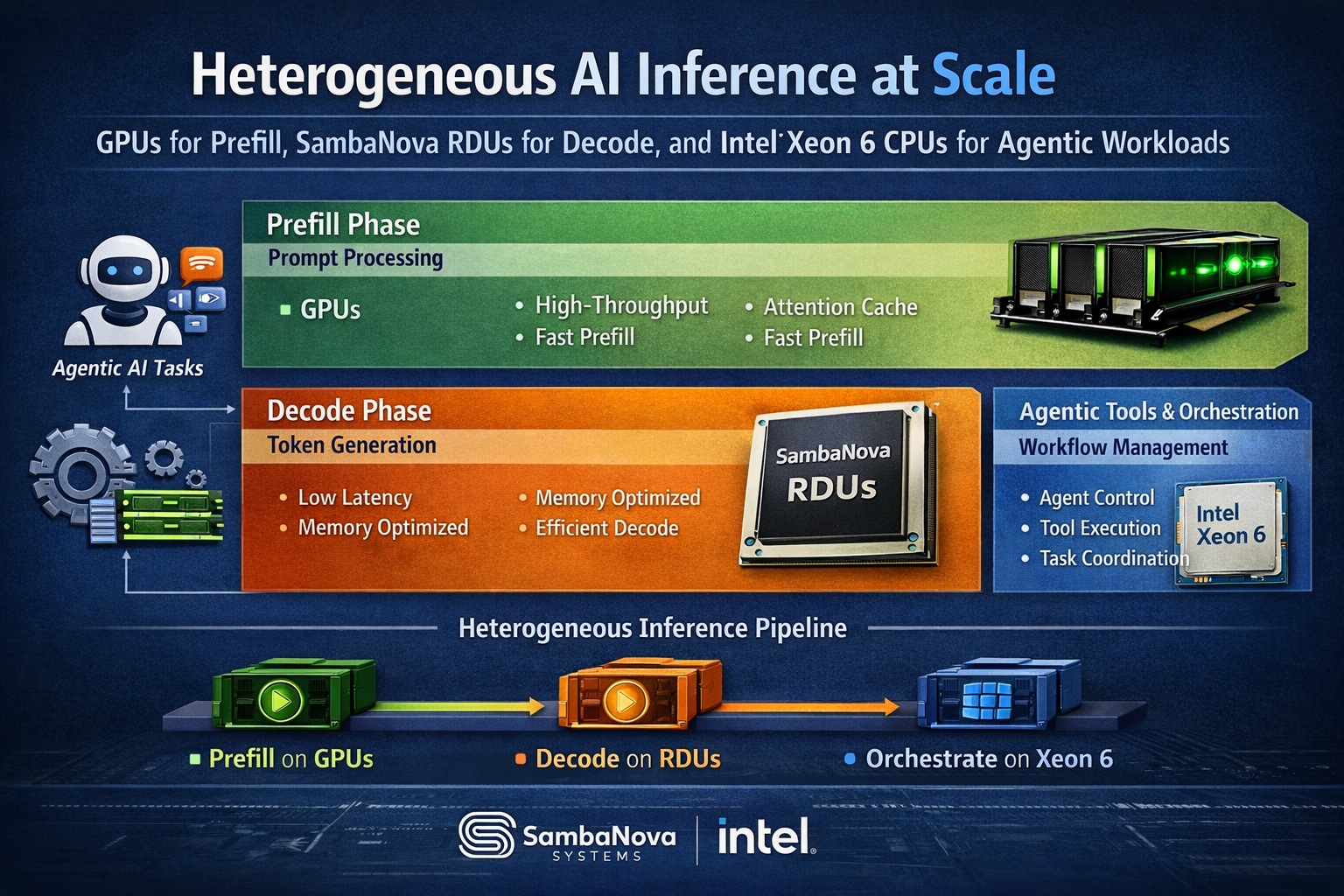

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More

CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More

TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read More

Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read MorePodcast EP104: Enabling Future Innovation with GBT Technologies

Dan is joined by Dr. Danny Rittman, CTO of GBT Technologies. Danny has an extensive background in the R&D space and has been working for companies such as Intel, IBM, and Qualcomm. He has spent most of his career researching and inventing processor chips, as well as paving the way for futuristic AI software programs that can be… Read More

Five Key Workflows For 3D IC Packaging Success

An earlier blog started with the topic of delivering 3D IC innovations faster. The blog covered the following foundational enablers for successful heterogeneous 3D IC implementation.

- System Co-Optimization (STCO) approach

- Transition from design-based to systems-based optimization

- Expanding the supply chain and tool

WEBINAR: Intel Achieving the Best Verifiable QoR using Formal Equivalence Verification for PPA-Centric Designs

Synopsys Fusion Compiler offers advanced optimizations to achieve the best PPA (power, performance, area) on today’s high-performance cores and interconnect designs. However, advanced transformation techniques available in synthesis such as retiming, multi-bit registers, advanced datapath optimizations, etc. are

A faster prototyping device-under-test connection

When discussing FPGA-based prototyping, we often focus on how to pour IP from a formative SoC design into one or more FPGAs so it can be explored and verified before heading off to a foundry where design mistakes get expensive. There’s also the software development use case, jumpstarting coding for the SoC before silicon … Read More

IC Layout Symmetry Challenges

Many types of designs, including analog designs, MEMs, and image sensors, require electrically matched configurations. This symmetry has a huge impact on the robustness of the design across process variations, and its performance. Having an electrically matched layout basically means having a symmetric layout. To check … Read More

Verifying 10+ Billion-Gate Designs Requires Distinct, Scalable Hardware Emulation Architecture

In a two-part series, Lauro Rizzatti examines why three kinds of hardware-assisted verification engines are a must have for today’s semiconductor designs. To do so, he interviewed Siemens EDA’s Vijay Chobisa and Juergen Jaeger to learn more about the Veloce hardware-assisted verification systems.

What follows is part one,… Read More

GM: Where an Option is Not an Option

How does a General Motors executive react when they get a transfer to work at OnStar? “What am I going to tell my partner?”

Twenty-six years after its founding, OnStar remains an appendage to GM – a team set apart from the heart and soul of the larger company. Team members assert that the group is profitable, thanks to millions of GM… Read More

C-V2X: Talking Cars: Toil & Trouble

Last year, the U.S. Federal Communications Commission sought to resolve the lingering dispute over the use of 75MHs of Wi-Fi spectrum in the 5.9MHz range, previously allocated to the automotive industry for safety applications, by designating 45MHz of that spectrum for unlicensed use while preserving 30MHz for automotive … Read More

Podcast EP103: A Look at the Game-Changing Technology Being Built by Luminous Computing

Dan is joined by Michael Hochberg, president at Luminous Computing. His career has spanned the space between fundamental research and commercialization for over 20 years. He founded four silicon photonics companies garnering a total exit value of over a billion dollars.

Dan explores the computing technology being built by … Read More

Is Intel About to Take Flight?