It’s all around us. The pervasive use of AI is changing our world. From planetary analysis of weather patterns to monitoring your vital statistics to assess health, it seems as though smart everything is everywhere. Much has been written about the profound impact AI is having on our lives and society. Everyone seems to agree that… Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read More

Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read MoreWebinar: Semifore Offers Three Perspectives on System Design Challenges

The exponential increase in design complexity is a popular topic these days. In fact, it’s been a topic of discussion for a very long time. The explosion of chip and system design complexity over the past ten years has become legendary and haunts many of us daily. A lot of the complexity we face has to do with coordinating across an ever-increasing… Read More

Today’s SoC Design Verification and Validation Require Three Types of Hardware-Assisted Engines

Lauro Rizzatti offers Semiwiki readers a two-part series on why three kinds of hardware-assisted verification engines are now a must have for semiconductor designs continues today. His interview below with Juergen Jaeger, Prototyping Product Strategy Director in the Scalable Verification Solution division at Siemens EDA,… Read More

Why China hates CHIPS

The CHIPS and Science Act has its fair share of critics, with detractors calling it corporate welfare for “losers” like Intel, or lacking guardrails to prevent companies making legacy chips in China.

One of the most vocal opponents of the act has been China’s communist-ruled government.

MAB: The Future of Radio is Here

Good story telling is what helps drive change, engage consumers, and define progress. Steve Newberry, CEO of Quu, is a master of the craft.

He told two stories, in particular, at the Michigan Association of Broadcasters event last week in Traverse City, Mich. The first story was to simply note for the broadcasters in attendance

Podcast EP105: Cadence STA Strategy and Capabilities, Today and Tomorrow with Brandon Bautz

Dan is joined by Brandon Bautz, senior group director of product management responsible for silicon signoff and verification product lines in the Cadence Digital & Signoff Group. Brandon has more than 20 years of experience in chip design and the EDA industry and has been at Cadence for over 10 years.

Dan explores the current… Read More

The Semiconductor Cycle Snowballs Down the Food Chain – Gravitational Cognizance

-Where are we in the chip cycle? Why is it different this time?

-No one rings a bell to indicate the top or bottom of a cycle

-Could the lack of self-awareness lead to a worse downturn?

-Who will weather the cycle better & come out on top

Gravitational Cognizance

“A cartoon character will not fall until they realize they should

… Read More

Resilient Supply Chains a Must for Electronic Systems

The last few years have seen multiple disruptions in the supply chain in many industries. One of the key technologies that many fingers have pointed to is the semiconductor technology. As products in all industries become more electronics based, semiconductors play a key role since no end system could function today without … Read More

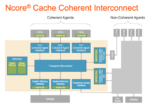

Coherency in Heterogeneous Designs

Ever wonder why coherent networks are needed beyond server design? The value of cache coherence in a multi-core or many-core server is now well understood. Software developers want to write multi-threaded programs for such systems and expect well-defined behavior when accessing common memory locations. They reasonably expect… Read More

Podcast EP104: Enabling Future Innovation with GBT Technologies

Dan is joined by Dr. Danny Rittman, CTO of GBT Technologies. Danny has an extensive background in the R&D space and has been working for companies such as Intel, IBM, and Qualcomm. He has spent most of his career researching and inventing processor chips, as well as paving the way for futuristic AI software programs that can be… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?