I’ve been following Solido as a start-up EDA vendor since 2005, then they were acquired by Siemens in 2017. At the recent User2User event there was a presentation by Kwonchil Kang, of Samsung Electronics on the topic, ML-enabled Statistical Circuit Verification Methodology using Solido. For high reliability circuits… Read More

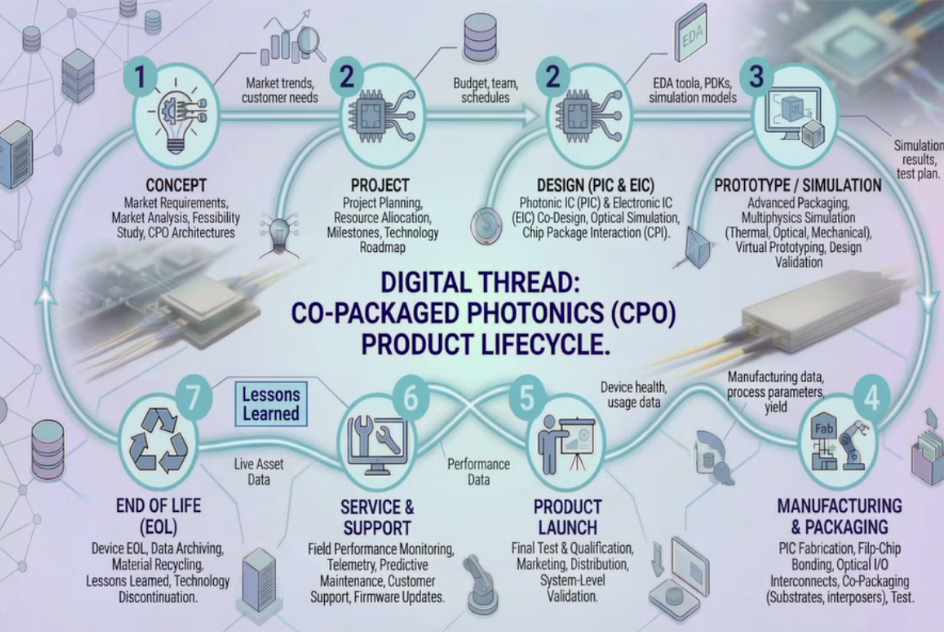

yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More

yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More

RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read MoreGate Resistance in IC design flow

MOSFET gate resistance is a very important parameter, determining many characteristics of MOSFETs and CMOS circuits, such as:

• Switching speed

• RC delay

• Fmax – maximum frequency of oscillations

• Gate (thermal) noise

• Series resistance and quality factor in MOS capacitors and varactors

• Switching speed and uniformity… Read More

Achieving Optimal PPA at Placement and Carrying it Through to Signoff

Performance, Power and Area (PPA) metrics are the driving force in the semiconductor market and impact all electronic products that are developed. PPA tradeoff decisions are not engineering decisions, but rather business decisions made by product companies as they decide to enter target end markets. As such, the sooner a company… Read More

Anirudh Keynote at Cadence Live

Anirudh is an engaging speaker with a passion for technology. Acknowledging the sign of the times, he sees significant value-add in AI but reminded us that it is a still supporting actor in system design and other applications where star roles will continue to be played by computational software that’s founded in hard science, … Read More

Formal-based RISC-V processor verification gets deeper than simulation

The flexibility of RISC-V processor IP allows much freedom to meet specific requirements – but it also opens the potential for many bugs created during the design process. Advanced processor features are especially prone to errors, increasing the difficulty and time needed for thorough verification. Born out of necessity, … Read More

Podcast EP159: The Fourth Quarter ESDA Market Data Report with Dr. Walden Rhines

Dan discusses the recent Q4 2022 ESDA report with Wally Rhines, Executive Sponsor of the SEMI Electronic Design Market Data report. Overall, the report portrays strong growth and positive results. Dan explores some anomalies in the data and possible reasons with Wally.

Dan also discusses some very interesting events at the upcoming… Read More

Petri Nets Validating DRAM Protocols. Innovation in Verification

A Petri nets blog scored highest in engagement last year. This month we review application of the technique to validating an expanding range of JEDEC memory standards. Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue… Read More

Podcast EP158: The Benefits of a Unified HW/SW Architecture for AI with Quadric’s Nigel Drego

Dan is joined by Nigel Drego, the CTO and Co-founder at Quadric. Nigel brings extensive experience in software and hardware design to his role at Quadric. Nigel is an expert in computer architectures, compiler technology, and software frameworks.

Dan explores the unique and unified HW/SW architecture developed by Quadric with… Read More

CEO Interview: Ravi Thummarukudy of Mobiveil

Mobiveil Marks 11th Anniversary

Ravi Thummarukudy is Mobiveil’s Chief Executive Officer and a founder. He and I recently spent an enjoyable afternoon getting acquainted as I learned more about Mobiveil. It’s an inspiring story of a technology company in the semiconductor space helping customers and prospering.

Eleven-year-old… Read More

TSMC 2023 North America Technology Symposium Overview Part 5

TSMC also covered manufacturing excellence. The TSMC “Trusted Foundry” tagline has many aspects to it, but manufacturing is a critical one. TSMC is the foundry capacity leader but there is a lot more to manufacturing as you will read here. Which brings us to the manufacturing accomplishments from the briefing:

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea