LLMs have amazing capabilities but inference run times grow rapidly with the size of the input (prompt) sequence, a significant weakness for some applications in engineering. State space models (SSMs) aim to correct this weakness. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur,… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read MoreDefect-Pattern Leveraged Inherent Fingerprinting of Advanced IC Package with TRI

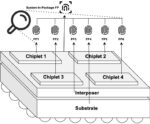

In the quest to secure the authenticity and ownership of advanced integrated circuit (IC) packages, a novel approach has been introduced in this paper that capitalizes on the inherent physical discrepancies within these components. This method, distinct from traditional strategies like physical unclonable functions (PUFs)… Read More

Podcast EP256: How NoC Tiling Capability is Changing the Game for AI Development with Andy Nightingale

Dan is joined by Andy Nightingale, VP of product management and marketing at Arteris. Andy has over 37 years of experience in the high-tech industry, including 23 years in various engineering and product management positions at Arm.

Dan explores with Andy the significance of the recently announced tiling capabilities and extended… Read More

How to Update Your FPGA Devices with Questa

It’s a fact of life that technology marches on. Older process nodes get replaced by newer ones. As a result, ASSPs and FPGAs are obsoleted, leaving behind large system design investments that need to re-done. Since many of these obsolete designs are performing well in the target application, this re-do task can be particularly … Read More

Overcoming obstacles with mixed-signal and analog design integration

Mixed-signal and analog design are key aspects of modern electronics. Every chip incorporates some form of analog IP, as even digital logic is dependent on analog signals for critical functions. Many digital design engineers are known to be uncomfortable with the prospect of integrating analog components. However, the current… Read More

Emerging Growth Opportunity for Women in AI

I was invited to the Fem.AI conference in Menlo Park, the first sponsored by the Cadence Giving Foundation with a goal to promote increased participation of women in the tech sector, especially in AI. Not just for equity, also to grow the number of people entering the tech/AI workforce. There are countless surveys showing that demand… Read More

LRCX- Coulda been worse but wasn’t so relief rally- Flattish is better than down

- Lam put in good quarter with flattish guide- still a slow recovery

- This is better than worst case fears of order drop like ASML

- China spend is slowing but tech spending increase offsets

- Relief rally as the market was braced for bad news and got OK news

Lam has OK, slightly better than in line quarter with OK guide….

It coulda been… Read More

Podcast EP255: The Growing Proliferation of Semiconductors and AI in Cars with Amol Borkar

Dan is joined by Amol Borkar, Product Marketing Director at Cadence. Since joining in 2018 as a senior product manager, he has led the development of many successful hardware and software products, including Tensilica’s latest Vision 331 and Vision 341 DSPs and 4DR accelerator targeted for various vision, automotive and AI edge… Read More

CEO Interview: Sean Park of Point2 Technology

Sean Park is a seasoned executive with over 25 years of experience in the semiconductors, wireless, and networking market. Throughout his career, Sean has held several leadership positions at prominent technology companies, including IDT, TeraSquare, and Marvell Semiconductor. As the CEO, CTO, and Founder at TeraSquare,… Read More

From Space-Central to Space-Time Balanced – A Perspective for Moore’s Law 2.0 and A Holistic Paradigm for Emergence

A friend of SemiWiki published an article on Moore’s Law in IEEE that I think is worth reading:

IEEE Signal Processing Magazine, Vol. 41, Issue 4.

The topic of Moore’s Law is of paramount importance, reaching almost the entire field of electronics (and the semiconductor industry). In the course of six decades, for the first… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!