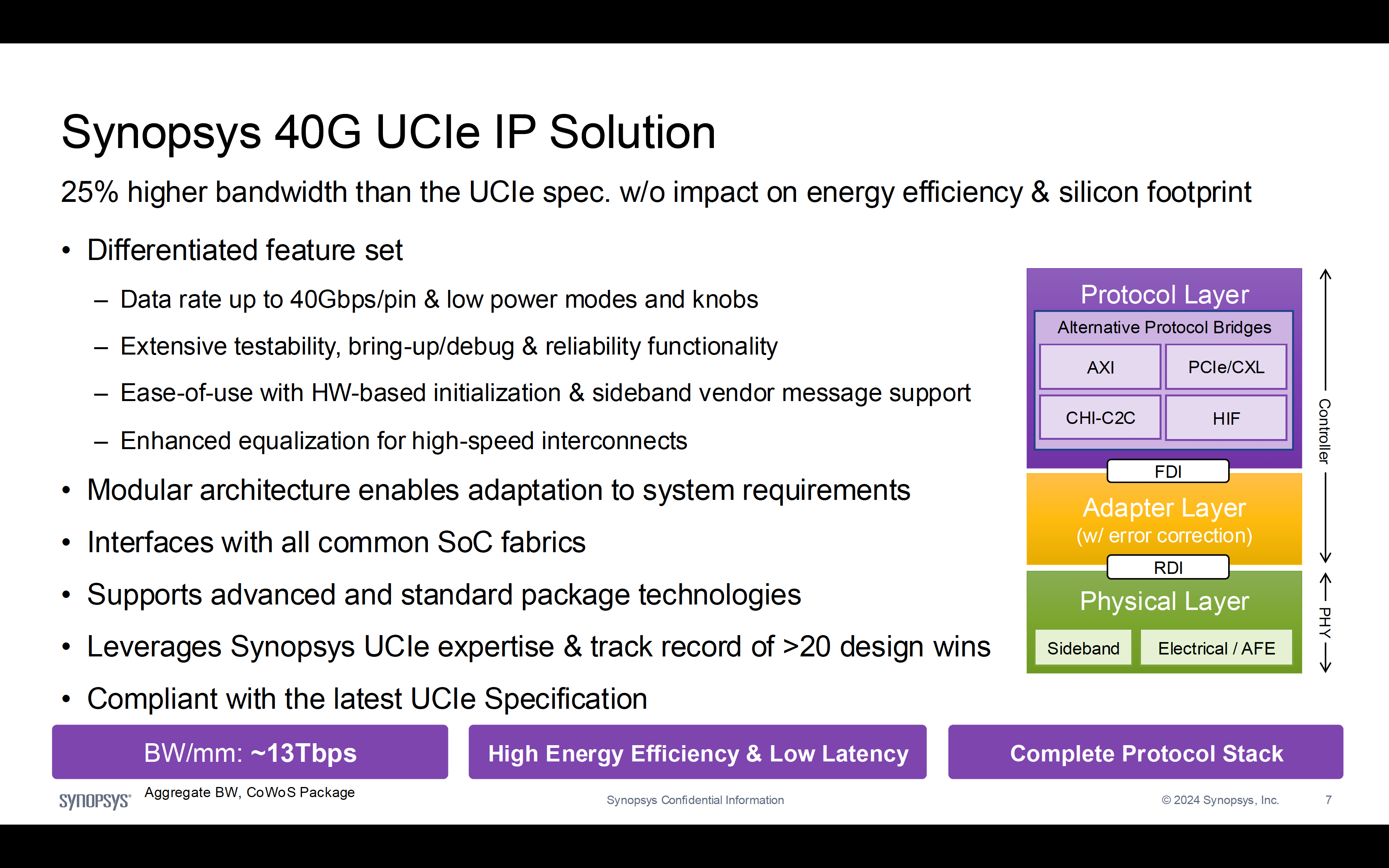

As the demand for higher performance computing solutions grows, so does the need for faster, more efficient data communication between components in complex multi-die system-on-chip (SoC) designs. In response to these needs, Synopsys has introduced the world’s fastest UCIe-based IP solution, capable of operating at a groundbreaking 40Gbps. This full IP solution, encompassing Controller, PHY, and Verification IP, represents a leap forward for die-to-die connectivity in SoCs, targeting data centers, AI, generative AI, and a wide array of cutting-edge applications.

What sets this solution apart is that it achieves 40Gbps per pin, a 25% increase over the 32Gbps defined in the UCIe specification, without compromising energy efficiency or die area. This capability opens up new possibilities for end users while maintaining seamless integration with the UCIe ecosystem.

During a chat with Michael Posner, vice president of IP product management at Synopsys, he commented that their active contribution to the UCIe consortium is what enabled the company to deliver a robust UCIe solution soon after the UCIe 2.0 ratification. Delivering robust IP solutions ahead of a standard’s ratification has become routine for Synopsys as noticed with Ethernet 1.6T and PCIe 7.0 IP solution announcements.

The UCIe Advantage: An Industry Standard for Die-to-Die Connectivity

Universal Chiplet Interconnect Express (UCIe) has emerged as the de facto standard for die-to-die connectivity, offering a scalable solution for high-performance, multi-die designs. The key metrics of UCIe — bandwidth per mm², power efficiency, low latency, and minimal area usage — align perfectly with the needs of customers across various industries, from data centers to AI applications.

Why 40Gbps?

Synopsys’ new IP solution is UCIe compliant at 32Gbps per pin and goes beyond it, offering speeds up to 40Gbps per pin in specific use cases. By increasing the data transfer rate to 40Gbps, the company ensures that multi-die SoCs can efficiently handle the growing data requirements in these environments. While pushing the boundaries beyond the UCIe specification, the solution is able to provide more bandwidth without impacting the energy or area budgets of the design. This is particularly leverageable and beneficial in environments where dies are tightly linked, such as in multi-die architectures that need to efficiently transfer massive amounts of data between SoC components. The additional bandwidth provided by the 40Gbps solution allows system designers to future-proof their designs while meeting current demands.

Modular Architecture for Scalable Bandwidth

A significant advantage of this UCIe IP solution is its modular architecture. The PHY component of the IP consists of 64 Tx and 64 Rx lanes, which can be combined to create large-scale solutions with substantial bandwidth. This makes the solution ideal for memory-intensive applications, such as those using high-bandwidth memory (HBM) chiplets. In these designs, high-speed die-to-die communication is essential to ensure the performance of memory subsystems. The Synopsys UCIe solution’s 40Gbps capability offers an extra margin of performance for these applications, ensuring that memory bandwidth requirements are not only met but exceeded, allowing for greater flexibility in SoC design. This flexibility allows designers to optimize for both area and performance, achieving high data throughput without sacrificing valuable chip real estate.

“Heterogeneous integration with high-bandwidth die-to-die connectivity gives us the opportunity to deliver new memory chiplets with the efficiency needed for data-intensive AI applications,” said Jongwoo Lee, vice president of the System LSI IP Development Team at Samsung Electronics. “Leveraging Synopsys’ new 40G UCIe IP, we can extend our collaboration to develop industry-leading chiplet solutions for tomorrow’s high-performance data centers.”

With Synopsys’ solutions like PCIe 7.0 and Ethernet 1.6T already addressing the need for high-bandwidth data coming into SoCs, UCIe provides the means for that data to flow between dies seamlessly.

Signal Integrity Monitors: Enabling Reliable Mission-Critical Operations

The UCIe IP solution includes Signal Integrity Monitors which monitor the integrity of the links for identifying any degradation in performance. When any degradation is noticed, the system can be flagged for taking any proactive maintenance measures or the profiled information can be offloaded for further analysis.

The ability to assess link degradation and flag for corrective action before a failure occurs ensures higher reliability and reduces the risk of downtime. Synopsys 40G UCIe IP offers silicon lifecycle management (SLM) features, where data from the profiling process can be used for longer-term reliability assessments. A proactive approach to reliability is especially important for industries like data centers and automotive, where continuous operation and safety are paramount. Further, this feature is expected to be a game-changer in industries like automotive, where real-time data integrity is also essential for reliable vehicle operations.

UCIe’s Redundant Links and Lifecycle Management

The UCIe specification defines redundant links to enhance reliability. Synopsys’ UCIe solution supports redundant links and links found to be defective can be rerouted to spare links during manufacturing or testing.

Simplified Clocking for Easy Integration

The company has further reduced system integration complexity by incorporating built-in clocking capabilities that make use of a 100MHz reference clock, a standard across SoC designs for many years. UCIe typically requires a 1GHz or 2GHz clock, but by integrating the capability to work with a more common 100MHz clock, the company has simplified system-level integration, allowing designers to adopt the technology more easily without the need for complex clocking inputs.

Hardware-Based Initialization: A Key Differentiator

Another unique aspect of the company’s UCIe-based IP is its hardware-based initialization, which eliminates the need for processor or firmware interaction during the bring-up process. The company has simplified this process by developing a system that allows the UCIe link to come online without external intervention, greatly reducing the complexity and cost associated with multi-die designs.

This capability is particularly important in “blind die bring-up” scenarios, where the only connection between two dies is the UCIe link. By eliminating the need for firmware or processor involvement in establishing the link, the company reduces the need for complex software solutions, saving time and reducing development costs.

Summary

With its new UCIe IP solution, capable of operating at 40Gbps per pin, Synopsys has advanced die-to-die communication technology for high-performance AI SoCs. By delivering 25% more bandwidth than the UCIe specification without impacting energy or area, the company is enabling designers to meet the needs of today’s data-intensive applications, while ensuring scalability for future generations.

The modular architecture, integrated Signal Integrity Monitors and test features, protocol bridges and simplified clocking provide a robust, scalable solution for high-bandwidth, low-latency SoC designs. As industries continue to shift towards multi-die architectures, the company’s 40Gbps UCIe IP offers a powerful tool for system designers looking to optimize performance, reliability, and ease of integration.

Read the full press announcement here.

To learn more, visit Synopsys UCIe solution page.

Also Read:

Synopsys IP Processor Summit 2024

Mitigating AI Data Bottlenecks with PCIe 7.0

The Immensity of Software Development the Challenges of Debugging (Part 1 of 4)

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.