It is well-known that AI is upending conventional wisdom for system design. Workload-specific processor configurations are growing at an exponential rate. Along with this is an exponential growth in data bandwidth needs, creating an urgency for 1.6T Ethernet. A recent SemiWiki webinar dove into these issues. Synopsys and Samtec explored many of the challenges to face on the road to extreme data bandwidth.

An example is the critical role of 224G SerDes in enabling high-speed data transfers and the importance of rigorous interoperability testing across all parts of the channel. Other topics are covered, including a look at what comes after 1.6 Terabits per second (Tbps). A replay link is coming but first let’s look at what’s discussed in the webinar – Achieving Seamless 1.6 Tbps Interoperability with Samtec and Synopsys.

The Speakers

The quality of most webinars is heavily influenced by the expertise of the speakers. For this webinar, there are two knowledgeable, articulate presenters that provide a great deal of valuable information.

Madhumita Sanyal is the director of technical product management for the high-speed Ethernet, PCIe, and D2D IP portfolio at Synopsys. She has over 20 years of experience in ASIC design and the application of logic libraries, embedded memories, mixed-signal IPs, and design methodology for SoCs in high-performance computing, automotive, and mobile markets.

Matt Burns develops go-to-market strategies for Samtec’s Silicon-to-Silicon solutions. Over the course of 25 years, he has been a leader in design, applications engineering, technical sales and marketing in the telecommunications, medical and electronic components industries. He currently serves as Secretary at PICMG.

Topics Covered

The webinar focused on the requirements for SoC design to achieve interoperability for the high bandwidth, high-performance computing required for AI/ML workloads. Madhumita and Matt cover a lot of topics, but they get through all of it in about 40 minutes. Very efficient. This is followed by approximately 15 minutes of live questions from the webinar audience. The topics covered are:

- Introduction

- Triggering new protocols like UAL for scale-up, and UEC for scale-out with an underlying line-rate of 224

- Why ecosystem enablement is important

- What capabilities in 224G SerDes can help achieve industry requirements for scale-up and scale-out

- Interconnect needed to build 224G data center system topologies

- Interop setup and demo

- 448G channel look-ahead

- Synopsys summary

- Samtec summary

- Q&A

Before I get into some more details, a definition of scale-up and scale-out would be useful.

Scale-up, also known as vertical scaling involves adding more resources to existing infrastructure to handle increased workloads. Scale-out, also known as horizontal scaling involves distributing workloads across multiple resources.

What follows are some highlights of the topics covered in the webinar.

What follows are some highlights of the topics covered in the webinar.

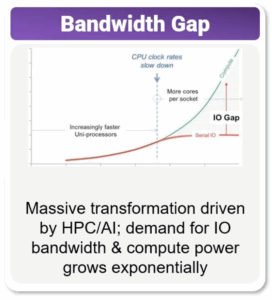

Madhumita began with an overview of the substantial bandwidth demands of new AI architectures. She referred to the bandwidth gap, as shown in the figure on the right. This increase cannot be addressed by doing more of what was done before. New architectures supported by new protocols are required as systems are both scaled-up and scaled-out.

She then provides a lot of details on how approaches such as Ultra-Ethernet and UALink_200 can help to address the challenges ahead. Madhumita provides details regarding various architectures that can achieve both scale-up and scale-out requirements. She discusses the various characteristics of passive copper cable, active copper cable and optical modules and where each fit.

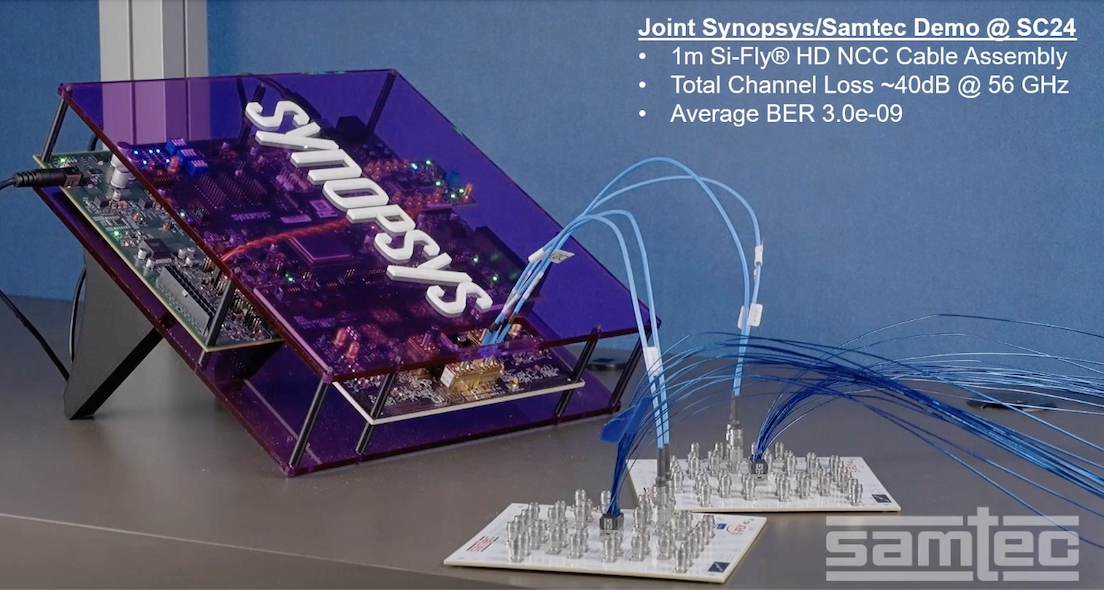

Both short and long reach capabilities for 224G channels are explored in detail with specific requirements for SerDes technology. Architectural details and waveforms are shared. She also covers the specific requirements of the simulation environment and the requirements of the models to drive the process. Madhumita concludes with an overview of the interoperability requirements of the Synopsys SerDes and the pallet of solutions offered by Samtec to complete the implementation. She shares a list of technologies that are used for interoperability validation that includes:

- 224G loopback with Samtec Si-Fly® HD Near Chip Cable Assembly 64 port, 40dB+ channels

- 24G loopback with 1m DAC + MCBs

- 224G electrical loopback with Samtec Si-Fly® HD Near Chip Cable Assembly 32 port, 40dB+ channels

- 224G electrical loopback with Samtec Bulls Eye® ISI Evaluation Boards

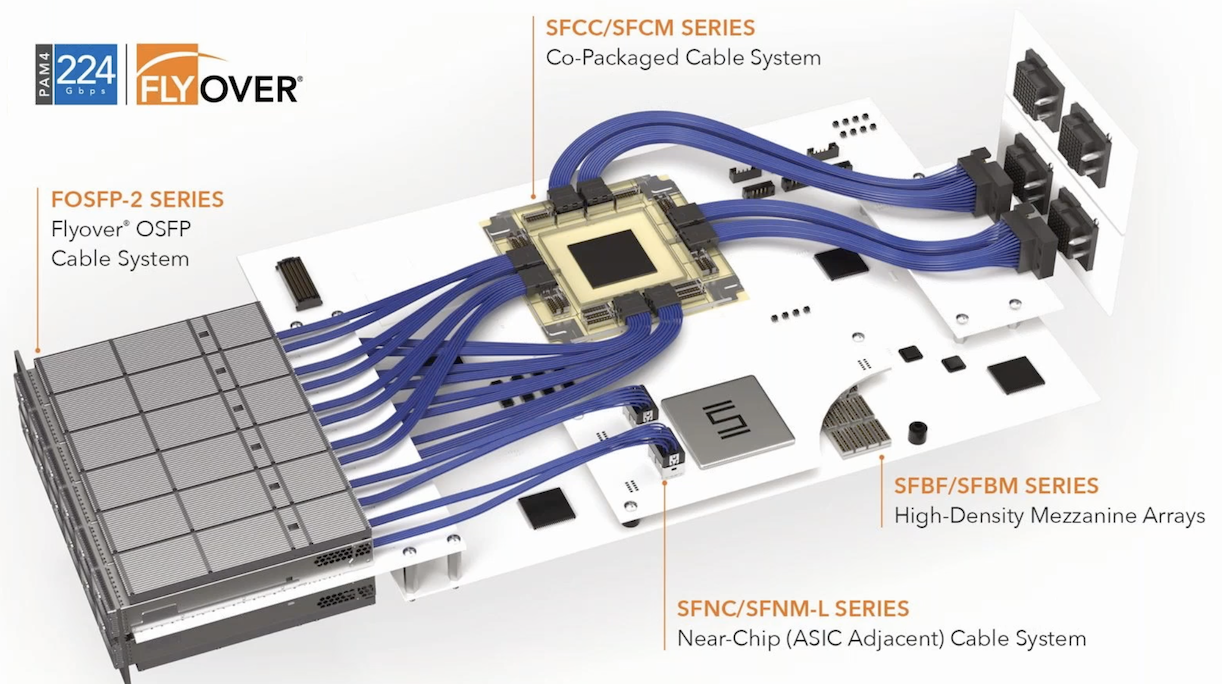

Matt then discusses the changes Samtec is seeing in system topologies in the data center, including disaggregated memory. Scalable, flexible, high-performance interconnect becomes a critical requirement. This is where Samtec is focused. Matt began with the diagram below that summarizes the various Samtec interconnect products that facilitate 224 Gbps PAM4 operation from the front panel to the backplane.

He spends some time explaining the various components in this diagram, both optical and copper as well as the benefits of Samtec Flyover® technology. The benefits of Samtec’s Si-Fly® HD co-packaged copper interconnects are also discussed. Some of the features Matt discusses in detail include:

- Ultra-high-density co-packaged substrate-to-cable

- Highest density interconnect supporting 224 Gbps PAM4 (170 DP/in2)

- Designed for high density interconnect (HDI) & package substrates

- Eye Speed® Hyper Low Skew Twinax cable technology supports 224 Gbps PAM4 signaling (32 AWG)

- Hyper low skew: 1.75 ps/meter max

Matt then provides detailed performance data for various Samtec interconnect configurations along with the architectural benefits of each approach. Both short and long reach configurations are discussed. Matt describes some of the work Samtec is doing with its OEM and OSAT partners to prove out various configurations.

Matt then provides details of a recent live demonstration with Synopsys to illustrate the interoperability of Synopsys communication IP and Samtec channel solutions.

Matt concludes with a discussion of the work underway for 448 Gbps channels. While still in development, Matt shares some details of what to expect going forward. Both Matt and Madhumita then finish with an overview of the capabilities of each company to address high-speed channels, both now and in the future. This is followed by a spirited Q&A session with questions from the live audience.

It Takes a Village

I had the opportunity to chat with Matt Burns a bit after the webinar. I’ve known Matt for a long time and always enjoy hearing his perspectives on the industry since Samtec typically looks at system design challenges a bit differently than a chip company. Matt began our discussion with this statement:

“If I’m an OEM or an ODM and I’m trying to implement 1.6T ports, there’s no one solution provider I can go to for the whole thing. It takes a village.”

Matt went on to describe the types of IP, physical channels, simulation models and methodology required to get the job done. In this situation, interoperability is key and that’s why working with leading companies like Synopsys is so important to Samtec. This is how real-world solutions are proven and adopted in the market. Matt felt a lot of the details of this formidable task are covered in the webinar, so now it’s time to access the webinar replay.

To Learn More

If AI is part of your next design, you will face the need for high-performance channels and the Samtec/Synopsys webinar delivers a lot of the details you will need. You can access the webinar replay here. And that’s the webinar – Achieving Seamless 1.6 Tbps Interoperability with Samtec and Synopsys.

Also Read:

Samtec Advances Multi-Channel SerDes Technology with Broadcom at DesignCon

2025 Outlook with Matt Burns of Samtec

Samtec Paves the Way to Scalable Architectures at the AI Hardware & Edge AI Summit

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.