As the Linley Fall Processor Conference winds down, there are certain presenting companies that left a lasting impression. SiFive is one of those companies. On October 21, SiFive introduced the newest member of the SiFive Intelligence family of processor coresSiFive Intelligence family of processor cores, based on the RISC-V ISA and the RISC-V Vector (RVV) extension. And then on October 29 they presented details of the highly anticipated RISC-V PC ecosystem. So, SiFive was busy expanding RISC-V technology and its ecosystem. Here are some details of both presentations.

As the Linley Fall Processor Conference winds down, there are certain presenting companies that left a lasting impression. SiFive is one of those companies. On October 21, SiFive introduced the newest member of the SiFive Intelligence family of processor coresSiFive Intelligence family of processor cores, based on the RISC-V ISA and the RISC-V Vector (RVV) extension. And then on October 29 they presented details of the highly anticipated RISC-V PC ecosystem. So, SiFive was busy expanding RISC-V technology and its ecosystem. Here are some details of both presentations.

Extending AI SoC Design Possibilities Through Linux-Capable Vector Processors

This presentation was given by Krste Asanović, SiFive Chief Architect & Co-Founder and Co-Inventor of RISC-V. Krste began with a review of the challenges associated with AI SoC design. These include:

- Multiple bandwidth-hungry subsystems

- Multiple proprietary instruction sets for deep learning accelerators

- Poor memory-bandwidth utilization

- Complex memory crossbar

- Power optimization difficult to implement

There are also software challenges for these designs, including:

- Multiple proprietary accelerator instruction sets

- Multiple proprietary API’s and outdated libraries

- New techniques such as deep compression or Winograd transform not supported

- Memory hierarchy doesn’t match new algorithm requirements

- Poor compiler support, requires programming at a low level

- Power optimization difficult to implement

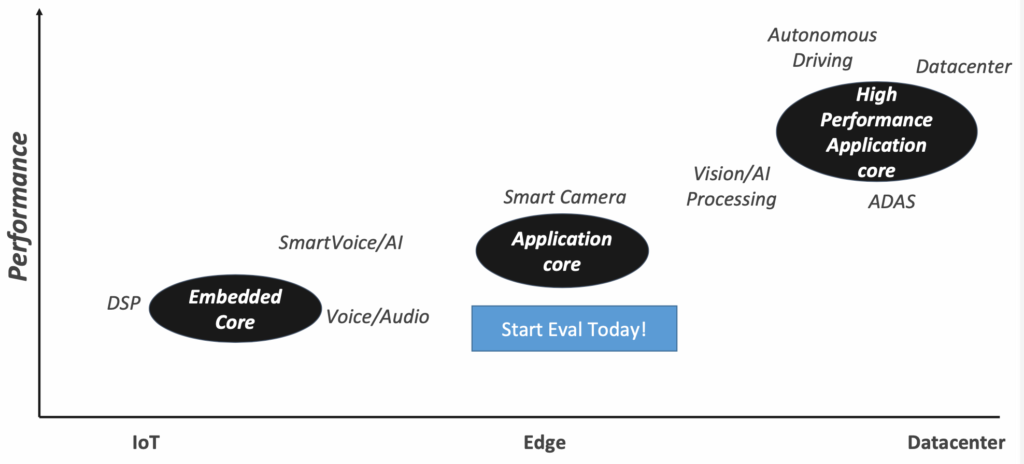

Krste then presented the newest member of the SiFive Intelligence family of processor cores to address these challenges. The family is based on an open industry standard ISA (RVV v1.0) to prevent vendor lock-in and enable rich ecosystem for AI. Krste reported this is the first commercially available processor core IP based on the expected final RVV 1.0 specification.

He explained these cores deliver scalable performance to meet AI processing requirements from extremely low power to high performance compute applications. The multi-core architecture can integrate Linux capable or real-time cores with accelerators to provide performance scaling. It also provides efficient memory hierarchy that maximizes data reuse. The single ISA enables a simple and efficient programming model that allows tuning algorithms for both performance and low power.

Security is always a discussion point for these applications, and SiFive provides comprehensive security support enabled by SiFive WorldGuard, a capability of SiFive Shield to provide true hardware isolation for whole SoC security while enabling software portability. You can see a video overview of SiFive WorldGuard here. There is also an advanced trace and debug solution, making the Intelligence family quite robust. Krste shared the roadmap for this technology, shown below.

Creating a RISC-V PC Ecosystem for Linux Application Development

This presentation was given by Dr. Yunsup Lee, SiFive CTO & Co-Founder and Co-Inventor of RISC-V. Yunsup detailed what embedded developers need, which includes:

- Industry Standard Form Factor

- Advanced Features

- Linux-Capable Development Platform

- Out-of-the Box Software

- IP Evaluation

- Expansion

Yunsup explained that SiFive delivers these capabilities with its HiFive Unmatched, a development board for a Linux-based PC that uses its RISC-V processors. A photo of the development board and a summary of key features is shown below.

Yunsup detailed some of the capabilities of the SiFive FU740 SoC on this board. These include:

- SiFive 7-Series Multi-Core Application Processor

- 64-Bit 8-Stage Dual-Issue, Superscalar RISC-V Core

- Application Core Complex

- 4x SiFive U74 Cores

- RV64GC (RV64IMAFDC)

- 32KB I$ Per Core

- 32KB D$ Per Core

- Single Embedded S7 Core

- RV64IMAC

- 16KB I$

- 8KB DTIM

- 2MB Coherent Banked L2$

- Integrated PCIe® Gen 3, DDR4, & I/O

Yunsup mentioned a short video demonstration of HiFive Unmatched used as a professional developer platform. He explained the video will cover:

- Native compilation

- Video application

- Example benchmark

- GPU accelerated video playback

- Web browser functionality

The video was posted to the SiFive YouTube channel after the presentation and can be viewed here.

Also available is the Freedom E SDK, which is a repository of demo programs, industry standard benchmarks and board support packages (BSPs) for SiFive’s hardware platforms. The package is available on GitHub here. Yunsup explained the development board will be available worldwide Q4’20 for $665USD. So, SiFive was indeed busy expanding RISC-V technology and its ecosystem.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.