Synopsys recently unleashed Fusion Compiler™, a new RTL-to-GDSII product that enables a data-driven design implementation by revamping Design Compiler architecture and leveraging the successful Fusion Technology –seamlessly fusing the logical and physical realms to produce predictable QoR. It is a long-awaited move that provides a breakthrough solution as more designers are migrating into deep advanced nodes, 7nm and beyond.

Synopsys recently unleashed Fusion Compiler™, a new RTL-to-GDSII product that enables a data-driven design implementation by revamping Design Compiler architecture and leveraging the successful Fusion Technology –seamlessly fusing the logical and physical realms to produce predictable QoR. It is a long-awaited move that provides a breakthrough solution as more designers are migrating into deep advanced nodes, 7nm and beyond.

Let’s glance through earlier synthesis key challenges that might act as precursors to subsequent developments leading towards this vital product announcement.

Traditional synthesis challenges

As part of the RTL-to-GDSII flow, synthesis tool such as Design Compiler transforms design RTL description into an optimized gate-level representation. This includes performing architectural, logic and gate level optimization steps. Synthesis utilizes standard cell library, pre-characterized for timing and power across various input slews, load conditions and process corners (or PVT –Process, Voltage, Temperature), to generate optimal design based on a given set of PPA (Performance, Power and Area) target. Over time, synthesis has been fitted with limited physical and placement awareness as inroad into routing.

As wire performance fails to keep pace with device performance in advanced process scaling, inadequate interconnect modeling or estimation has translated to a disparity between the synthesis QoR and those generated by downstream physical implementation tools. The once tolerable trade-off across PPA during micrometer process node era is no longer acceptable for sign-off in advanced nodes –as designs are increasingly being targeted for emerging applications that require power efficiency as well.

Interconnect shift impacts not only on delay related metric, but also on power due to the increased RC or degraded-slew induced power dissipation. Such gap has been exacerbated by device threshold lowering or near threshold condition that shifts the total power contribution from dynamic to the static term. This drives the need of having a solution that delivers optimal results for both performance and power.

Moreover, increased design density also has strained synthesis tool and has demanded scalability, runtime improvements and more physical awareness. For example, the tool needs not only a congestion awareness but also a capability for generating legalized placement –to ascertain an accurate resource utilization and minimal perturbation during route optimization.

Common Data Model and Fusion Technology

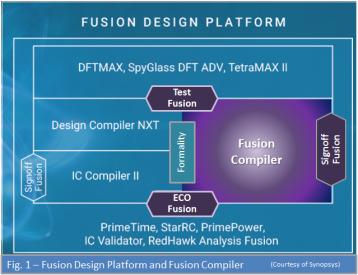

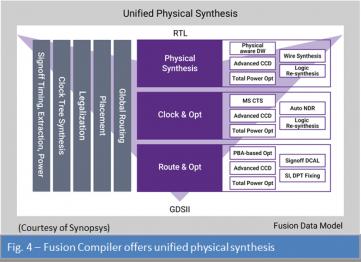

Key to this breakthrough is the adoption of a common data-centric architecture. The Fusion Compiler single data model contains both logical and physical information to enable sharing of library, data, constraints, and design intent throughout the implementation flow. It has scalability to support ultra-large designs with the smallest feasible memory footprint. The Fusion Data Model serves all design phases and provides faster tool-data model interaction, interactive what-if analysis, and native multi-everything (cores, corners, etc.) with near-linear scalability across multiple CPU cores. It also supports transparent, multi-level hierarchy and the efficiency to run compute-intensive algorithms, facilitating more optimizations for better QoR.

Key to this breakthrough is the adoption of a common data-centric architecture. The Fusion Compiler single data model contains both logical and physical information to enable sharing of library, data, constraints, and design intent throughout the implementation flow. It has scalability to support ultra-large designs with the smallest feasible memory footprint. The Fusion Data Model serves all design phases and provides faster tool-data model interaction, interactive what-if analysis, and native multi-everything (cores, corners, etc.) with near-linear scalability across multiple CPU cores. It also supports transparent, multi-level hierarchy and the efficiency to run compute-intensive algorithms, facilitating more optimizations for better QoR.

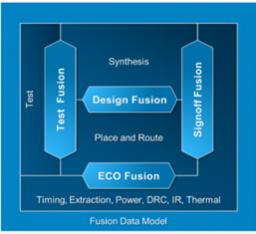

Another enabler is Synopsys Fusion Technology™ which was announced in March 2018. It provides new level of integration of Synopsys synthesis, place & route and signoff tools, by redefining conventional product boundaries with systematic sharing of algorithms, code and data representations across multiple tasks.

Another enabler is Synopsys Fusion Technology™ which was announced in March 2018. It provides new level of integration of Synopsys synthesis, place & route and signoff tools, by redefining conventional product boundaries with systematic sharing of algorithms, code and data representations across multiple tasks.

Fusion provides Design Fusion, ECO Fusion, Signoff Fusion, and Test Fusion technologies. Design Fusion enables synthesis technology inside place-and-route, and place-and-route technology inside synthesis. ECO Fusion drives faster signoff closure with the signoff analysis and ECO optimization enabled directly from within implementation. Signoff Fusion eliminates design margin and over-design, using PrimeTime and StarRC for both optimization and signoff. Test Fusion is the combination of design-for-test (DFT), synthesis and automatic pattern generation (ATPG) technologies. Using physical design data, Test Fusion ensures optimal placement of test points while minimizing routing congestion and area impact.

Fusion Technology offers a bidirectional access between synthesis and the adjoining implementation tools, including sharing of optimization engines between the two domains. As Fusion Compiler integrates all synthesis, place-and-route and signoff engines on a single data model, it removes the necessity of having data conversion and transfer –hence, providing good QoR accuracy, best predictability and optimal throughput.

The Fusion Design Platform also AI-enhanced to enable additional QoR and TTR gains by speeding up computation-intensive analyses, predicting outcomes to improve decision-making, and leveraging past learning to drive better results.

Fusion Compiler QoR and Customer Feedback

The unified architecture of Fusion Compiler shares technologies across the RTL-to-GDSII flow delivering 20 percent better QoR and 2X faster time-to-results (TTR). It has been silicon-proven at several customers.

Fusion Compiler’s new solver-based global optimization engine enables path-based total negative slack (TNS) targets and analysis of critical path traces for effective design closures. Both pre- and post-route engines use the same costing and infrastructure for consistent correlation throughout the flow. Its underlying multi-corner multi-mode (MCMM) and multi-voltage (MV)-aware heuristic algorithms concurrently tackle all the design metrics for best QoR. Likewise, logic remapping, rewiring and legalization interleaved with placement minimizes congestion and speeds timing closure. The CTS engine follows a networking flow paradigm for optimal balancing of latency and skew.

“The power of this technology is essential for the design of tomorrow’s FinFET-based automotive applications. With Fusion Compiler, we achieved the target design goal and completed the tapeout. Compared to conventional technology, we confirmed a 33 percent reduction in timing violations, 10 percent area reduction, and 30 percent less leakage power, while cutting the design turnaround time in half. We have completed the integration of Fusion Compiler in Toshiba’s design environment and have begun to deploy it to upcoming SoC designs,” said Seiichi Mori, senior vice president, Toshiba Electronic Devices and Storage Corporation.

“The power of this technology is essential for the design of tomorrow’s FinFET-based automotive applications. With Fusion Compiler, we achieved the target design goal and completed the tapeout. Compared to conventional technology, we confirmed a 33 percent reduction in timing violations, 10 percent area reduction, and 30 percent less leakage power, while cutting the design turnaround time in half. We have completed the integration of Fusion Compiler in Toshiba’s design environment and have begun to deploy it to upcoming SoC designs,” said Seiichi Mori, senior vice president, Toshiba Electronic Devices and Storage Corporation.

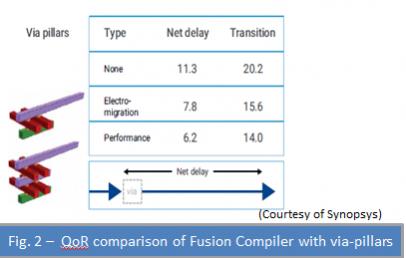

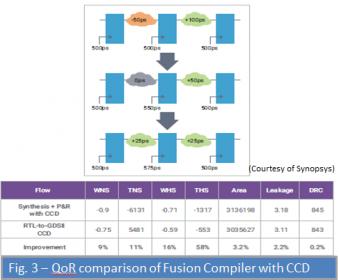

As shown in figure 2 and 3, Fusion Compiler runs produced more optimal PPA results from improved via-pillars handling and CCD (Concurrent Clock Data) optimizations –two snapshots of many underlying technological enhancements that promote the overall QoR gain.

“As design complexity increases across all our market segments, our key requirement is to achieve the best product performance coupled with the highest levels of predictability,” said Michael Goddard, senior vice president, Samsung SARC and ACL. “With Fusion Compiler, we are on track to achieve optimal PPA with up to 10 percent better timing, 10 percent lower leakage, two-to-five percent dynamic power savings, and typically two-to-three percent area reduction for our most challenging design blocks on our imminent tapeout. In addition, the predictable path from synthesis to signoff reduces design iterations, ensuring that we can meet our aggressive product schedules.”

“Strong semiconductor market drivers like autonomous driving and the adoption of AI continue to drive global demand for larger, faster, and more energy-efficient SoCs”, said Sassine Ghazi, co-general manager of Synopsys’ Design Group.

“Our early assessment of Fusion Compiler shows significantly better full-flow predictability, faster full-flow turnaround time, and better timing QoR compared to the previous approaches. We are collaborating with Synopsys to deploy this innovative RTL-to-GDSII solution, as it will streamline physical design of our mission-critical projects and allow us to bring new products to market much faster,” said Taichiro Sasabe, general manager, SoC Design Division at Socionext.

With this release of Fusion Compiler, Synopsys has raised the bar for a holistic synthesis solution –replacing the traditional RTL-to-GDSII design flow that is comprised of either disconnected or loosely-coupled tools for emerging applications and advanced process nodes.

For Fusion Compiler whitepaper please check HERE and datasheet HERE.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.