Remember that thing called “real-time Linux”? Yeah, nobody else does either. As builds became configurable and clock speeds increased, embedded Linux manifested itself as fast enough for many applications – if a few other SoC details are addressed.

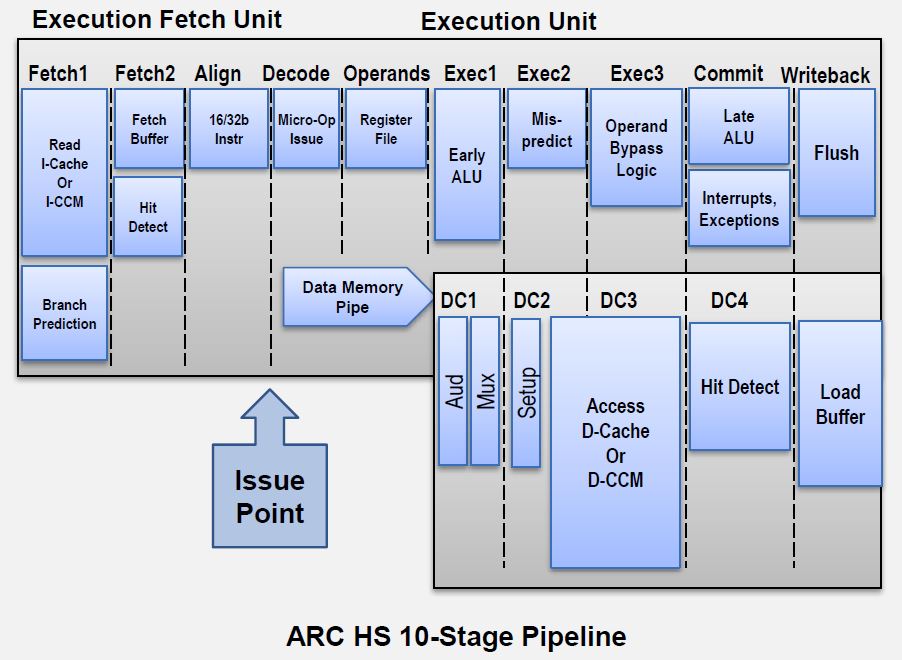

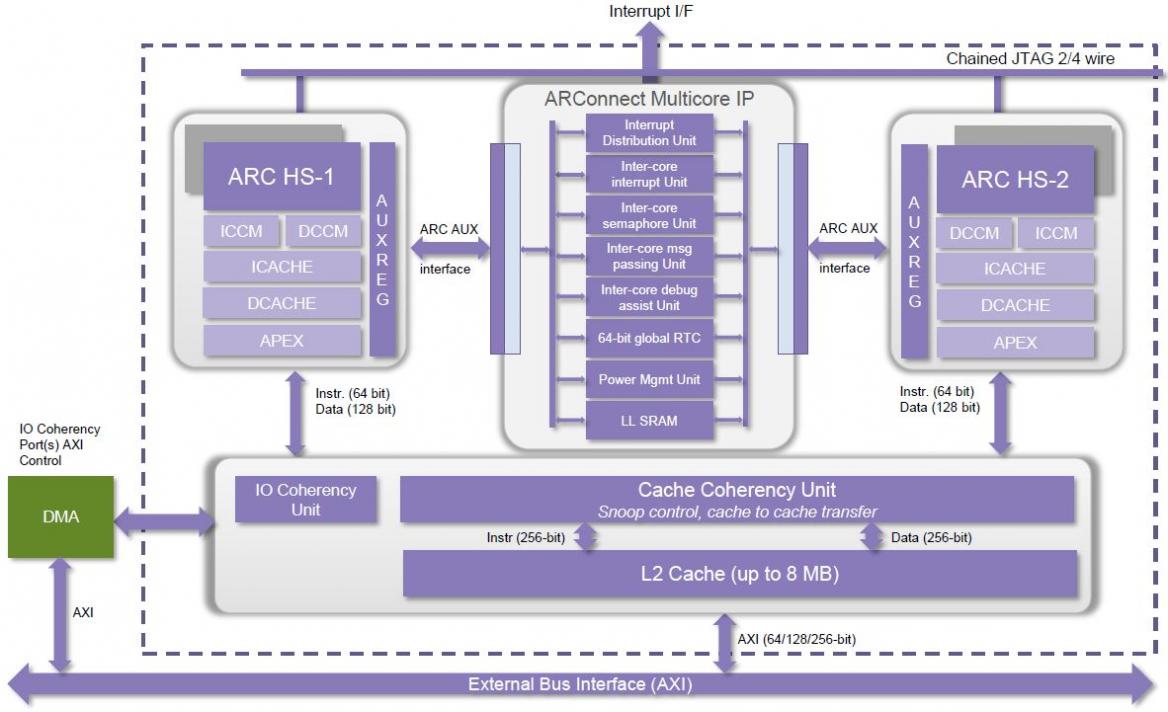

Most obvious for SoCs to run Linux is the need for a fully integrated MMU implementation. More importantly, as many RISC architecture teams have discovered the hard way over the years, cache coherency comes right to the top of the list. That implies both a snooping unit able to deal with multicore configurations, and enhancements to pipelining able to deal with both cache hits and misses efficiently.

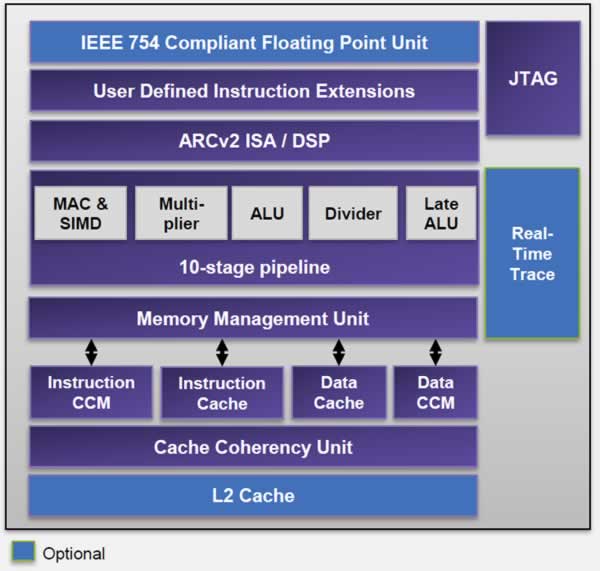

The Synopsys DesignWare ARC processor family has undergone a significant uplift with the move to the ARCv2 ISA. There are now two families in ARCv2: the EM for deeply embedded, ultra-low power applications; and the HS for high-speed applications.

With their recent announcement of the latest core, the ARC HS38, Synopsys strides into a new chapter. It’s not the first ARC member to support Linux; the ARC 770D was a single core ARCv1 unit with an MMU. Multicore support, a vastly improved pipeline, a flexible memory architecture with an enhanced MMU and closely coupled memory, cache coherency (first seen in the HS36), and more features make the ARC HS38 formidable.

Most designers that pick ARC do so for a combination of three reasons: low power, small die size, and extensibility. For me, the first thing that jumps off the page about the ARC HS38 is the power and area figures – 90mW at 2.2 GHz in 28nm, taking up only 0.21 mm[SUP]2[/SUP] of silicon. Mike Thompson, senior product marketing manager for ARC processors at Synopsys, said that power number “may be a little on the high side” for many implementations.

A second point is how good the pipeline is. I know we hear a lot of n-stage yada yada sometimes, but public details are often sparse. The 10-stage pipeline in the HS is delivering 1.9 DMIPS/MHz – on par with the ARM Cortex-A7. The HS38 is even better when the conversation shifts to DMIPS/mW.

The pipeline supports not only 16 MB of close coupled memory, but direct mapping of peripherals, amounting to single instruction register access for external resources once set up. We also see the stages dedicated to dealing with cache coherency. Wider 64-bit memory helps with bandwidth, and constraints on memory access time are relaxed for more cost effective system implementations. Support for L2 cache up to 8MB is included.

The enhanced MMU brings 40-bit physical addressing. It also adds large page size operations – 4MB, 8MB, and 16MB. An expanded virtual memory plus support for one, two, or four cores distinguishes the HS38 as a real embedded Linux engine. More details on the ARC HS38 are available at the Synopsys site.

For those users that have been extending ARC cores with user-defined instructions and RTL blocks, the HS38 is a welcome addition taking care of multicore and MMU needs. For new users looking to pack Linux in a power-efficient device, the HS38 is worth a look. Synopsys has all the tools, from compilers to embedded Linux to virtual platform models and FPGA-based prototyping, enabling a big leap in performance while still keeping power and die size small.

Comments

There are no comments yet.

You must register or log in to view/post comments.