No, I’m not going to talk about in-memory-compute architectures. There’s interesting work being done there but here I’m going to talk here about mainstream architectures for memory support in Machine Learning (ML) designs. These are still based on conventional memory components/IP such as cache, register files, SRAM and various… Read More

Tag: cache coherency

Neural Networks Leverage New Technology and Mimic Ancient Biological Systems

Neural networks make it possible to use machine learning for a wide variety of tasks, removing the need to write new code for each new task. Neural networks allow computers to use experiential learning instead of explicit programming to make decisions. The basic concepts related to neural networks were first proposed in the 1940’s,… Read More

CCIX shows up in ARM CMN-600 interconnect

All the hubbub about FPGA-accelerated servers prompts a big question about cache coherency. Performance gains from external acceleration hardware can be wiped out if the system CPU cluster is frequently taking hits from cache misses after data is worked on by an accelerator.

ARM’s latest third-generation CoreLink CMN-600 … Read More

How to Bring Coherency to the World of Cache Memory

As the size and complexity of System On Chip design has rapidly expanded in recent years, the need to use cache memory to improve throughput and reduce power has increased as well. Originally, cache memory was used to prevent what was then a single processor from making expensive off chip access for program or data memory. With the… Read More

Top Mobile OEM Uses NetSpeed to Boost Its Next Gen Application Processor

The smartphone segment is certainly the most competitive market for chip makers today and the yearly product launch cadence puts a lot of pressure on the application processor design cycle. End-users expect to benefit from higher image definition, better sound quality, ever faster and more complex applications which push the… Read More

Can you really address the Automotive market with AP designed for smartphone?

If you remember, when TI decided to exit the booming wireless segment in 2012, the company decided to re-focus their application processor product line (OMAP) initially developed for smartphone “to a broader market including industrial clients like carmakers”. Being a TI employee in the 90’s in south of France, where TI has started… Read More

SoCs should invest in a strong cache position

Like most technology firms, Apple has been home to many successes, and some spectacular defeats. One failure was Project Aquarius. At the dawn of the RISC era, before ARM architecture was “discovered” in Cupertino, engineers were hunkered over a Cray X-MP/48. The objective was to design Apple’s own quad core RISC processor to … Read More

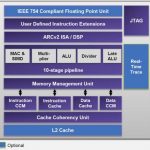

Linux and the ARC of the Coherent

Remember that thing called “real-time Linux”? Yeah, nobody else does either. As builds became configurable and clock speeds increased, embedded Linux manifested itself as fast enough for many applications – if a few other SoC details are addressed.

Most obvious for SoCs to run Linux is the need for a fully integrated MMU implementation.… Read More

DSPs converging on software defined everything

In our fascination where architecture meets the ideas of Fourier, Nyquist, Reed, Shannon, and others, we almost missed the shift – most digital signal processing isn’t happening on a big piece of silicon called a DSP anymore.

It didn’t start out that way. General purpose CPUs, which can do almost anything given enough code, time,… Read More