Digital verification engineers on SoC designs have adopted many techniques to help ensure first silicon success: using compiled simulators, constrained random test, simulation farms, SystemVerilog methodology, and self-checking testbenches. AMS verification has tended to be ad-hoc or sharply divided into separate analog verification and digital verification realms.

Synopsys has decided to start applying some of these digital verification techniques to mixed-signal designs in order to improve regression testing as announced today at SNUG. I spoke by phone last week with Steve Smith of Synopsys to hear about this new initiative, and it turns out that we worked together at CrossCheck back in the 90’s.

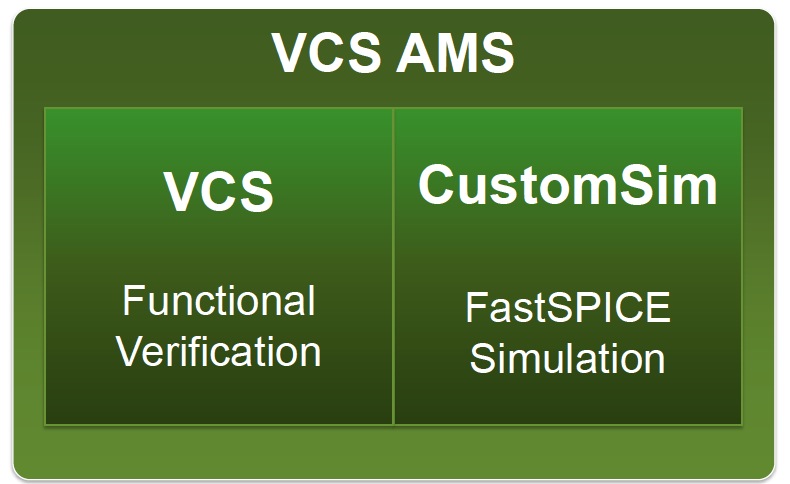

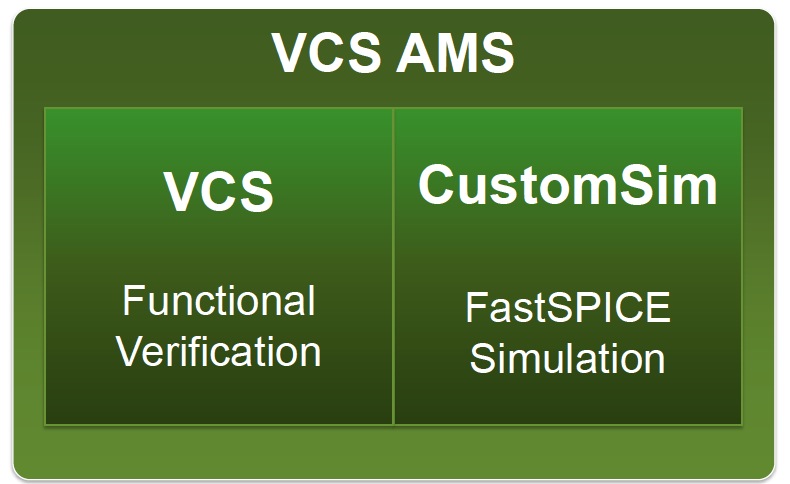

The first thing that comes to my mind when hearing about AMS verification is co-simulation between a digital and analog simulator. Synopsys has offered co-simulation technology for quite a while with their Discovery AMS tool that combined VCS for digital simulation, CustomSim for FastSPICE simulation at the transistor-level, plus a co-simulation interface. They’ve now created VCS AMS that efficiently co-simulates VCS and CustomSim together for AMS verification:

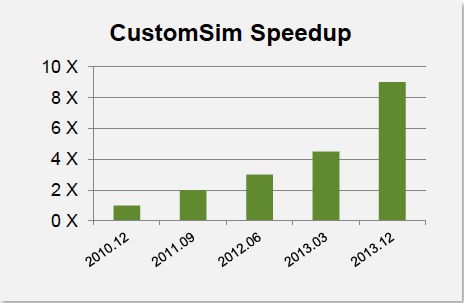

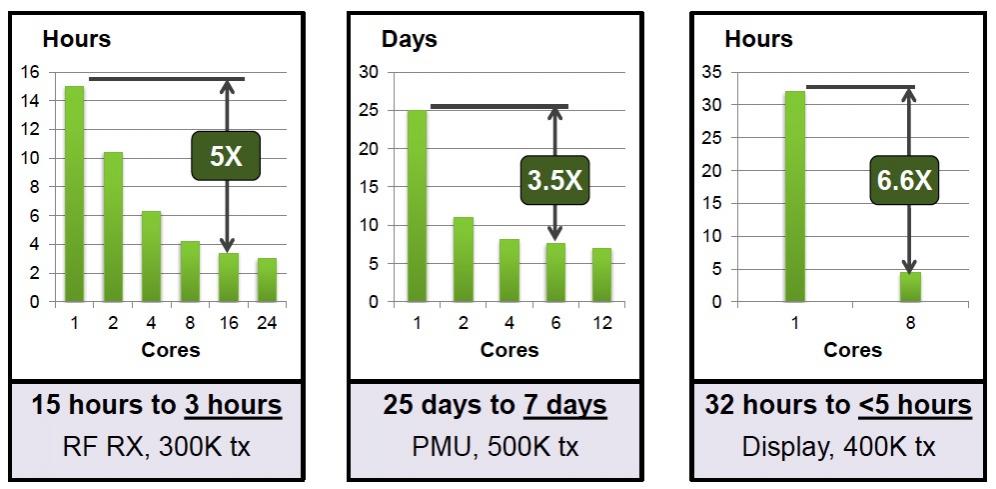

When verifying an AMS design with VCS AMS the bottleneck is typically the FastSPICE simulator, so it’s good to learn that CustomSim has been getting speed boosts over the past several years.

Using VCS AMS running on multi-core and server farms you can expect to see 3-5x speed ups.

The digital verification techniques that you can now use for mixed-signal designs are:

- Automatic connectivity between digital and analog blocks

- Real to Electrical (D2A)

- Electrical to Real (A2D)

- AMS assertions

- AMS constrained-random stimulus

- AMS checkers

- SystemVerilog real number modeling

- AMS testbench environment

- AMS source generators

- AMS functional coverage

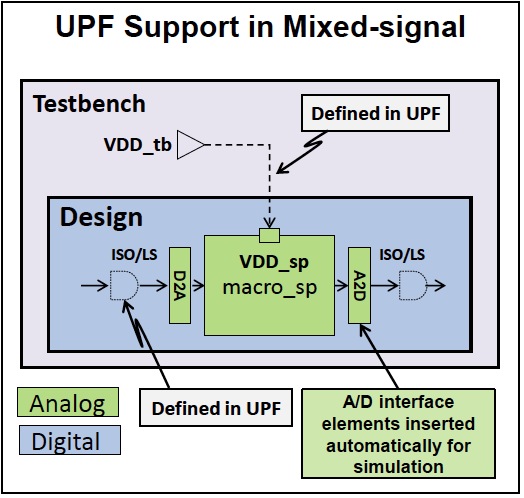

You can also define in UPF your mixed-signal design and get native low-power support, where the SPICE block appears as a digital block to UPF:

Two customers that are talking about using VCS AMS include Rambus (memory and interface IP) and Micronas (automotive and industrial). Three companies are presenting SNUG papers on their experiences with VCS AMS: ST Ericsson, AMD and KeyASIC.

Verification engineers using Synopsys simulators should look into this new initiative for their AMS SoC designs to speed up and improve their regression testing. The mindset is to start using the digital verification ideas in mixed-signal designs with a SystemVerilog testbench methodology.

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.