ARC is a family of configurable processors. Originally it was a standalone company in the UK (what is it with the UK and processor cores?) spun out from Argonaut Software. The A in ARC stood for Argonaut originally. ARC International was acquired by Virage and then Virage was acquired by Synopsys so now it is part of Synopsys Designware IP offering.

ARC is a family of configurable processors. Originally it was a standalone company in the UK (what is it with the UK and processor cores?) spun out from Argonaut Software. The A in ARC stood for Argonaut originally. ARC International was acquired by Virage and then Virage was acquired by Synopsys so now it is part of Synopsys Designware IP offering.

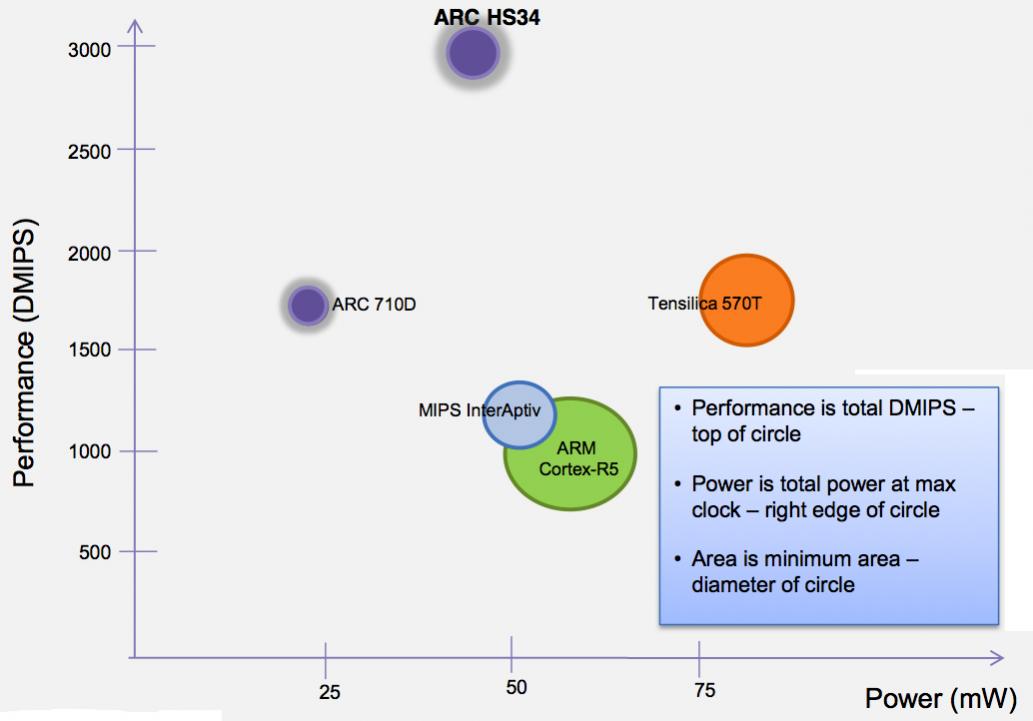

The family of cores has always been focused on low power and on configurability, but there has not been a high-performance core in the offering. Today Synopsys announced a new generation of high-speed processors, following a sneak preview at the Linley Microprocessor Conference a couple of weeks ago:

- advanced ARCv2 architecture

- 18% improvement in code density

- Real-time and high-end embedded focus

- >3000 DMIPS per core at under 60mW, 0.15mm[SUP]2[/SUP]

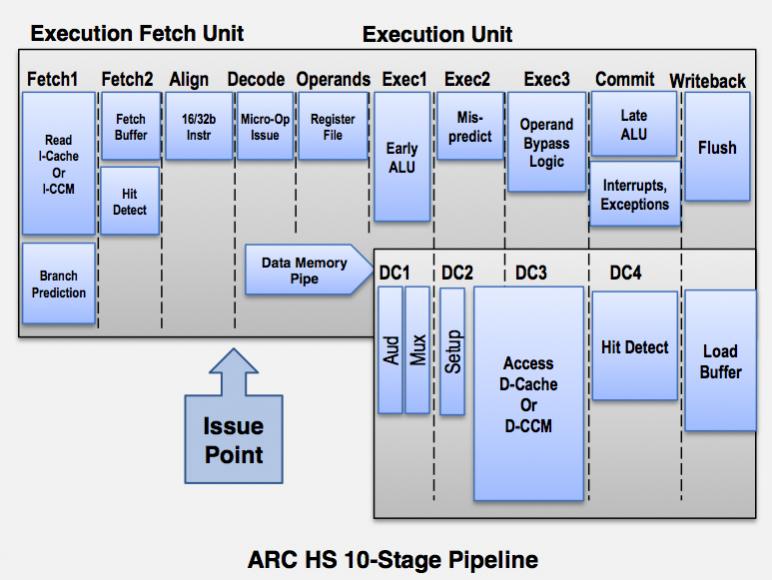

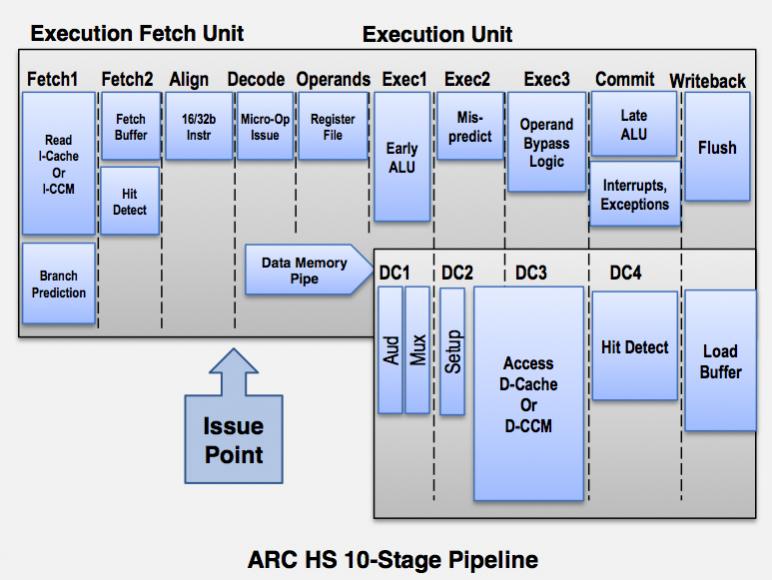

- power efficient 10-stage scalar pipeline

- out of order execution

- branch prediction

- late-stage ALU to improve throughput

- 64-bit loads and stores to move data

- 64-bit multiply and multiply-accumulate

- hardware integer divider (4 to 19 cycles)

- IEEE 754 compliant FPU with single/double precision

- ECC protection for all memories in processor

- I/O coherency for DMA and peripherals

From an implementation point of view, the new core makes less severe demands on the type of memories required on the chip. Only single-port SRAMs are required, even for the branch prediction cache. Two pipeline stages are dedicated to access CCMs and caches.

Compared to the older ARC cores such as the ARC700 there is a lot more throughput per megahertz and 50% higher CoreMark per megahertz. The maximum operating frequency is up from 1.1GHz to 1.6GHz. Also importantly, it can run and function at a clock rate as low as 2MHz, so offers lots of scope for dynamic frequency scaling for power saving.

The core is optimized for the high end embedded market such as automotive driver assist, solid state drives, digital TV, home networking and so on. Many of these have strong real-time requirements. So to get it:

- single-cycle peripheral and memory access

- fast context switch with a second register file

- configurable to hit sweet-spot for performance vs power

- custom instructions (as all ARC processors always have)

- robust interrupt architecture with up to 240 interrupts, 16 levels of priority, auto save and restore

- optional ECC hardware on all memories (to correct single event upsets etc)

Of course there is a full development tool chain. ARChitect optimized the processor and configures it. There is a range of compilers. ARC plays with virtual prototypes. Out of the box it has support for Linux and Android.

More details on ARC processors are on Synopsys’ website here.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.