Designing an LTE modem is an interesting case study in architectural and system level design because it is pretty much on the limit of what is possible in a current process node such as 28nm. I talked to Johannes Stahl of Synopsys about how you would accomplish this with the Synopsys suite of system level tools. He is the first to admit that this is not a push-button flow where everything flows cleanly from one tool to the next, but more of a portfolio of technologies that can be used to get a modem done. Another complication over previous generations is that multiple radios can be used simultaneously.

Designing an LTE modem is an interesting case study in architectural and system level design because it is pretty much on the limit of what is possible in a current process node such as 28nm. I talked to Johannes Stahl of Synopsys about how you would accomplish this with the Synopsys suite of system level tools. He is the first to admit that this is not a push-button flow where everything flows cleanly from one tool to the next, but more of a portfolio of technologies that can be used to get a modem done. Another complication over previous generations is that multiple radios can be used simultaneously.

LTE is actually a whole series of different standards with different uplink and downlink data rates, but one thing is constant: no matter what the data rate, the power dissipation of the modem must be such that the battery of the phone will last all day. So efficient tradeoff analysis is required to meet power and performance goals.

A high end LTE modem requires approximately 1 TOPS/second at 1W. To get there requires a complex architecture in which things happen in parallel. The picture above shows the type of architecture involved with dedicated FFT units and multiple SIMD execution units.

In principle it is possible to design a modem entirely in software, but the power dissipation would be unacceptably high. It is also possible to design highly optimized RTL but the design cycle would stretch out unacceptably and it would be too inflexible to cope with changes in the standards and the phone price points.

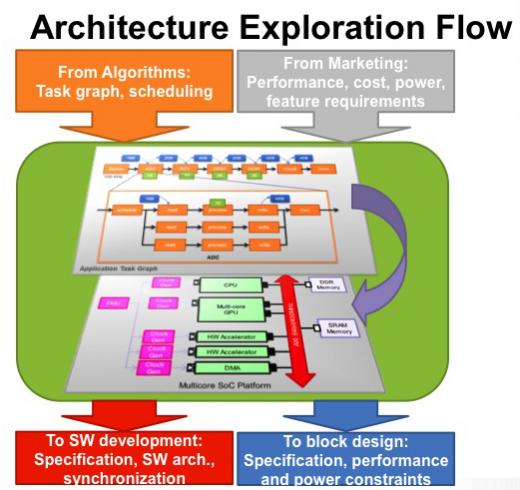

So step 1 is architectural exploration to answer questions such as:

- Application-level parallelism?

- How many cores?

- Which parts in HW and SW?

- Memory architecture?

- Interconnect topology?

- Performance, power?

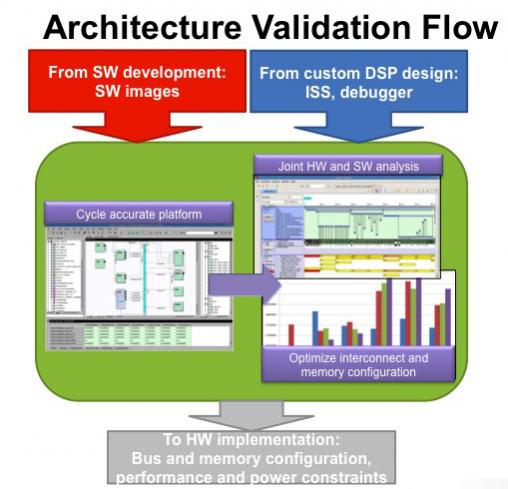

The verification of the architecture then requires a flow that takes both the basic block level architecture and the actual software loads as input, with a goal of refining the architecture so that the block level performance and power envelopes are defined, and the interconnectivity (such as bus widths) is determined. This can involve cycle accurate models, virtual platforms, Zebu emulation boxes and FPGA prototypes.

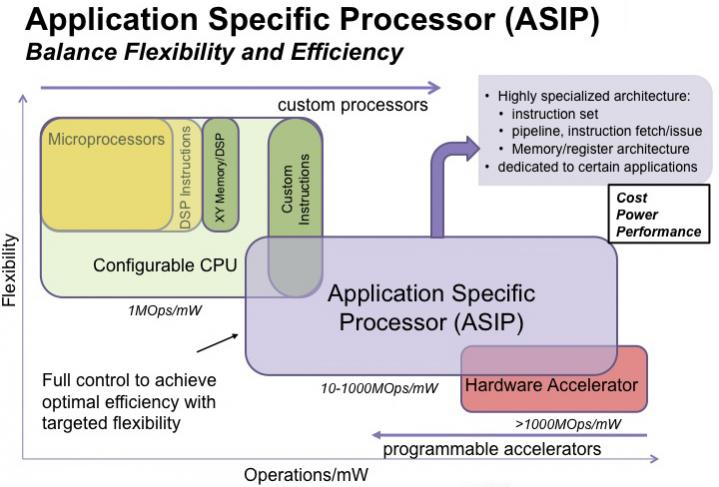

One possible type of block to include in the design is an application specific processor (ASIP). There are configurable processors that is one approach to modem design but it doesn’t necessary hit the sweet spot of PPA as well as an ASIP that can be created with Synopsys’s processor design tool (the old LISA that came to Synopsys via CoWare). The processor will require specialized functions useful for modems, for inverting matrices, error control coding (ECC) and so on.

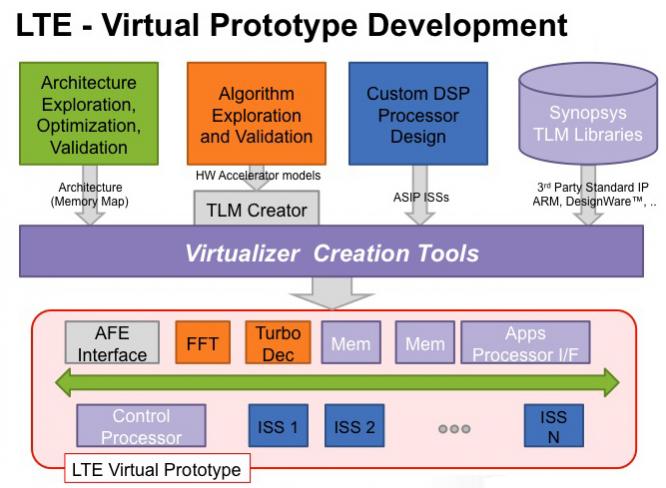

One nice side-effect of the model based approach is that at the end there is a virtual platform that can be used to accelerate software development before silicon is available (and perhaps after, since control and visibility is so much better in a virtual platform). Usually people don’t set out to change their software development methodology, but once the virtual platform is created for architectural reasons then it is ideal to use for the very complex debugging (involving several loads of software running on different processors: control processor, DSP software, protocol software, hardware etc, often all with their own debuggers).

This approach doesn’t make LTE modem design easy but it does at least make it possible.

More details on platform architect, processor developer,and virtualizer.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.