Still not convinced on the value of FPGA-based prototyping systems, or using older technology? I’ve been trying to find the story beyond just bigger, badder FPGAs in a box that you pour RTL into – and found some hints in a webinar on the Synopsys HAPS-70 from earlier this year.

The webinar, featuring Neil Songcuan, Sr. Product Marketing Manager for FPGA-based Prototyping Solutions at Synopsys, is here:

with people thinking they have already seen the product news, this webinar might have been overlooked, but it is worth revisiting. The bulk of the event is the product manager introducing a unique product and its key features, but he has several observations sprinkled in that I’ll focus on.

We’ve also covered the HAPS-70 previously here at SemiWiki; many of these concepts are also covered in the webinar.

Next Generation FPGA Prototyping, by Paul McClellan

Help, my IP has fallen and can’t get up, from my keyboard

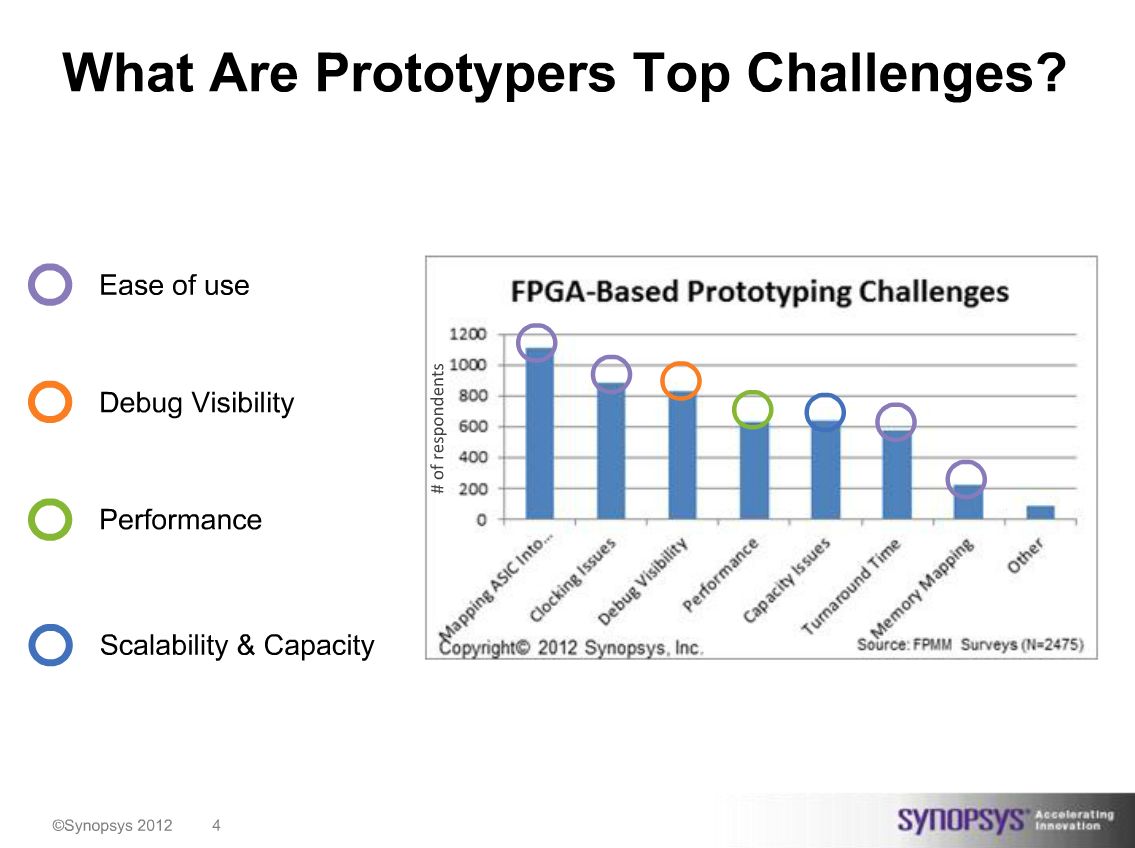

So, what new observations did I find in this HAPS-70 webinar? First is this chart, with a survey result from nearly 2500 users of FPGA-based prototyping:

The biggest concern developers have is mapping RTL across multiple FPGAs. We’ve talked about that one previously: manual partitioning is a risky and lengthy process on a huge design, especially given clocking and I/O complexity – automated tools are a must-have, and Songcuan addresses what Synopsys has done to help cut partitioning time from weeks to hours.

The debug visibility concern is also noteworthy. Sometimes, debug data is stored in internal memory of an FPGA. But, internal memory is a critical implementation resource, and often it gets consumed just in fitting the design, and nothing is left for debug. Songcuan outlines a simple but easily overlooked solution available in the HAPS-70.

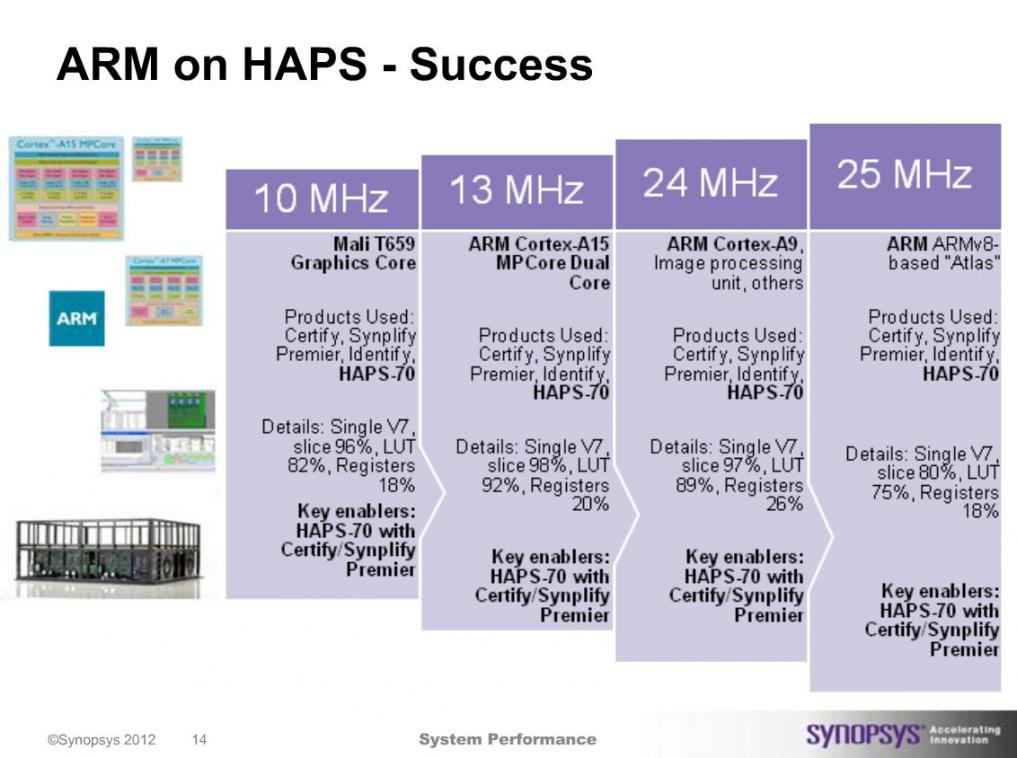

Notice that performance and capacity issues are only moderate concerns in those survey results – I think that is because developers can readily see that these systems are continuing to improve in speed and capacity. There is an interesting slide in this webinar showing performance data on various ARM cores implemented in a HAPS-70, addressing the question of how fast a design can go – for example, the answer for an ARMv8 “Atlas” 64-bit processing core is 25 MHz, plenty for software and system validation efforts.

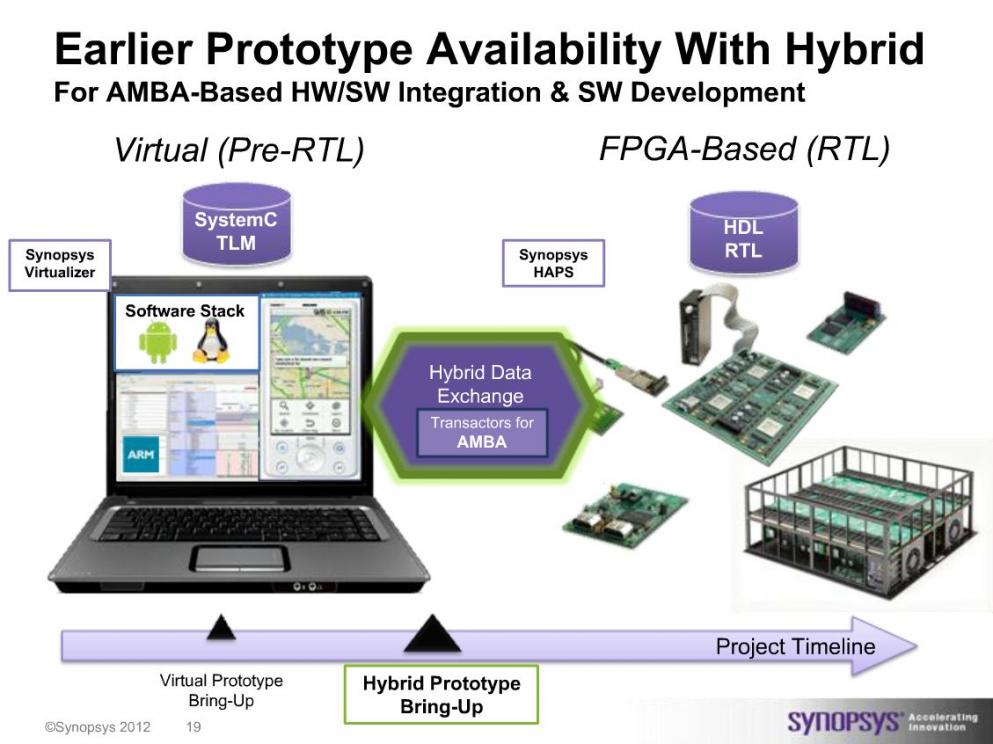

One important new concept Songcuan introduces is hybrid prototyping. Many developers, especially software teams using model-driven design, have adopted virtual prototyping using SystemC, and are also using FPGA-based prototyping in RTL. Those are often two wildly different tool sets and methodologies, separate acts in the development cycle. Synopsys has been concentrating on smoothing the process, particularly with hybrid data exchange transactors for AMBA. This allows a C model on a virtual prototype residing on a host to share information with the FPGA-based prototyping system.

One point Songcuan makes during the Q&A: emulators are still best for RTL verification, FPGA-based prototyping systems are designed for system and software validation. The latter is more cost effective for taking proven IP blocks and integrating them with actual application code, as opposed to applying test vectors and other verification strategies.

With an estimated 70% of ASIC designs taking advantage of FPGA-based prototyping platforms, it is interesting to see these systems starting to mature, with advanced packaging and interconnect strategies for bigger designs, better software tools, and more attention to integration with other pieces of the development flow.

lang: en_US

Share this post via:

Comments

0 Replies to “More to the story than bigger FPGA-based prototyping”

You must register or log in to view/post comments.