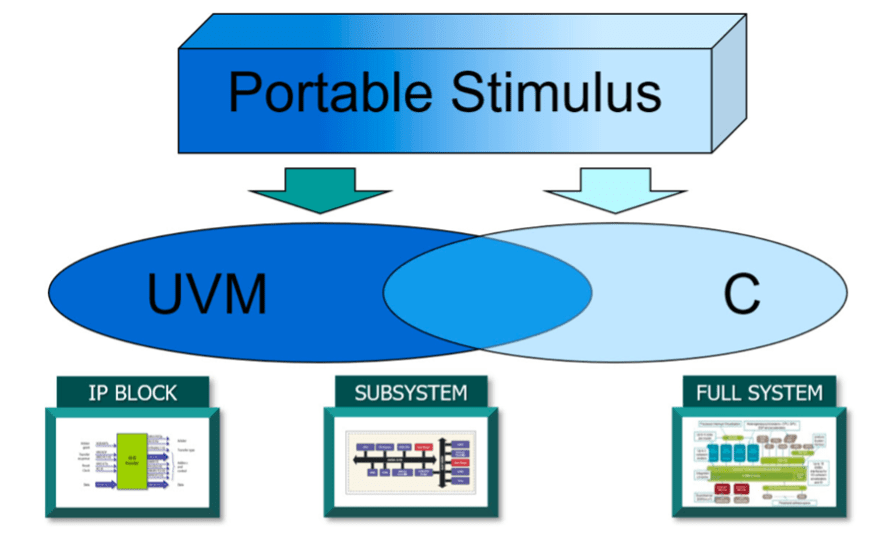

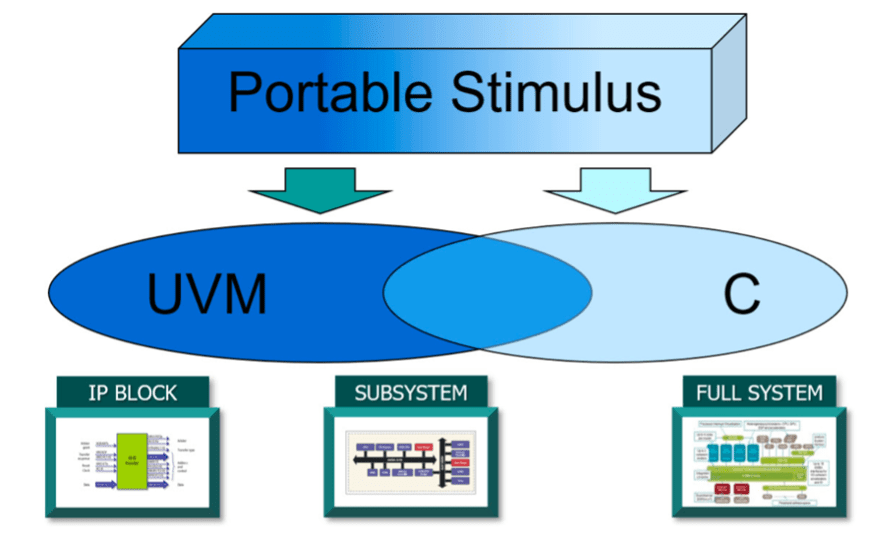

In the early days of the PSS rollout, some verification engineers were suspicious. Just as they were beginning to get comfortable with UVM, here came yet another standard to add to their learning and complexity overhead. Then the fog started to clear; UVM is ideal for block-level testing whereas PSS is ideal for system level testing. And the “P” in PSS is critical. UVM tests are portable into PSS test frameworks as are C tests running on a processor. All that effort put into developing detailed high coverage tests at the block level pays off also at the system level. Of course there should be some interoperability planning between the three test frameworks (PSS, UVM, C) but that was always the intent behind the standard. Siemens EDA have just released a white paper explaining how they recommend such a collaboration.

System-level test scenarios

Why can’t this all be handled in UVM with suitable sequences and randomization? Because what you need to test is simply too high-level and distributed to capture meaningfully in block-centric UVM sequences. Consider for example a multi-core processor cluster supported by coherent cache. Each processor is handling some task, and each is reading from and writing to memory through the cache. Which in turn must ensure a read access to any given logical address must return a consistent current value for that address, even if there is a pending (write) update to the same address from another processor.

Point being that behavior to be tested is distributed across multiple processors, caches (L1s and L2 for example) and a coherent NoC, already a complex state space. And when you build tests for such a system, you must account for factors which are meaningful in this sort of test: checking compliance with the expected coherence protocol (eg MOESI), handling write-through, accumulating stats for cache misses, detecting false sharing and so on. All very feasible in PSS but accommodating this would break your brain in UVM. Then randomization must randomize appropriate scenarios of read and write activity from the cores and cacheline states. While trying to break the protocol and memory consistency by stressing reads from/close to logical addresses for which writes are recent or pending.

There are many other system-level testing requirements: checking IO coherency, power management, interrupt handling, and more. All require modeling and randomizing synthetic or semi-real test scenarios running across distributed functions in a subsystem or system.

Folding in UVM and C

PSS is perfect for building and randomizing scenarios at this level, but these still must be connected to DUT-level testbench components. PSS orchestrates running detailed testing through connections to UVM virtual sequences or high-level C models, allowing you to easily coordinate between UVM and C components and to switch to alternate representations where appropriate as the design evolves. It can also help with testing on hybrid platforms, mixing software simulation, emulation and prototyping.

The white paper illustrates the application of their proposed approach with a couple of examples. The first shows a test methodology to verify writing and reading control/status registers in a block under control of a C routine running on a CPU, observing the interaction of register updates/read from the CPU with block functionality. This would be useful in testing development of a driver for example.

The second example outlines how you might build a VIP to test a DMA. While the previous case can also benefit from PSS randomization, this DMA example is a particularly obvious example of the advantages of a PSS approach. Activity between peripherals, memory and CPUs is unpredictable so randomization is especially important to explore traffic options and potential for collisions, starvation, etc. and to determine whether mechanism to mitigate such problems work effectively.

Nice paper. You can get access to the white paper HERE.

Also Read:

Heterogeneous 2D/3D Packaging Challenges

Averting Hacks of PCIe® Transport using CMA/SPDM and Advanced Cryptographic Techniques

Reset Domain Crossing (RDC) Challenges

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.