In the fast-evolving world of semiconductor design, creating a complex System-on-Chip (SoC) requires meticulous planning to ensure performance, power efficiency, and cost-effectiveness. Aion Silicon’s white paper, authored by Piyush Singh, outlines a streamlined methodology that leverages advanced modeling… Read More

Tag: c++

Moving Beyond RTL at #62DAC

Hardware designers have been using RTL and hardware description languages since the 1980s, yet many attempts at moving beyond RTL have tried to gain a foothold. At the #62DAC event I spent some time with Mike Fingeroff, the Chief High-Level Synthesis Technologist to understand what his company Rise Design Automation is up to. … Read More

Upcoming Webinar: Accelerating Semiconductor Design with Generative AI and High-Level Abstraction

We have been hearing so much lately about the power of AI and the potential of technologies like agentic AI to address the productivity gap and complexities of semiconductor designs of today and tomorrow. Currently, however, the semiconductor industry has been slow to adopt generative and agentic AI for RTL design code. There… Read More

PSS and UVM Work Together for System-Level Verification

In the early days of the PSS rollout, some verification engineers were suspicious. Just as they were beginning to get comfortable with UVM, here came yet another standard to add to their learning and complexity overhead. Then the fog started to clear; UVM is ideal for block-level testing whereas PSS is ideal for system level testing.… Read More

Something new in High Level Synthesis and High Level Verification

As SoC complexities continue to expand to billions of transistors, the quest for higher levels of design automation also rises. This has led to the adoption of High-Level Synthesis (HLS), using design languages such as C++ and SystemC, which is more productive than traditional RTL design entry methods. In the RTL approach there… Read More

New Tool that Synthesizes Python to RTL for AI Neural Network Code

AI and ML techniques are popular topics, yet there are considerable challenges to those that want to design and build an AI accelerator for inferencing, as you need a team that understands how to model a neural network in a language like Python, turn that model into RTL, then verify that your RTL matches Python. Researchers from CERN,… Read More

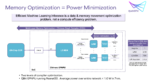

Quadric’s Chimera GPNPU IP Blends NPU and DSP to Create a New Category of Hybrid SoC Processor

Performance, Power and Area (PPA) are the commonly touted metrics in the semiconductor industry placing PPA among the most widely used acronyms relating to chip development. And rightly so as these three metrics greatly impact all electronic products that are developed. The degree of impact depends of course on the specific … Read More

PSS and Reuse: Great Solution But Not Hands-Free

If you’re new to PSS you could be forgiven for thinking that it automagically makes stimulus reusable, vertically from IPs to systems, horizontally between derivatives and between hardware-based and software-based testing. From a big-picture point of view these are certainly all potential benefits of PSS.

What PSS does provide… Read More

Konica Minolta Talks About High-Level Synthesis using C++

In the early days of chip design circa 1970’s the engineers would write logic equations, then manually reduce that logic using Karnaugh Maps. Next, we had the first generation of logic synthesis in the early 1980’s, which read in a gate-level netlist, performed logic reduction, then output a smaller gate-level netlist.… Read More

Easing Your Way into Portable Stimulus

The Portable Stimulus Standard (PSS) was officially released at DAC this year. While it will no doubt continue to evolve, for those who were waiting on the sidelines, it is officially safe to start testing the water. In fact it’s probably been pretty safe for a while; vendors have had solutions out for some time and each is happy to … Read More