Amid the alphabet soup of inter-die/chip coherent access protocols, CXL is gaining a lot of traction. Originally proposed by Intel for cross-board and cross-backplane connectivity to accelerators of various types (GPU, AI, warm storage, etc.), a who’s who of systems and chip companies now sits on the board, joined by an equally impressive list of contributing members. The standard enables coherent memory sharing between a central processor/CPU cluster with its own cache coherent memory subsystem, with memory/caching on each of multiple accelerator systems. This greatly simplifies life for software developers since memory consistency is managed in hardware. No need to worry about this in software; it’s all just one unified memory model, whether software is running on the processor or on an accelerator.

CXL and PCIe

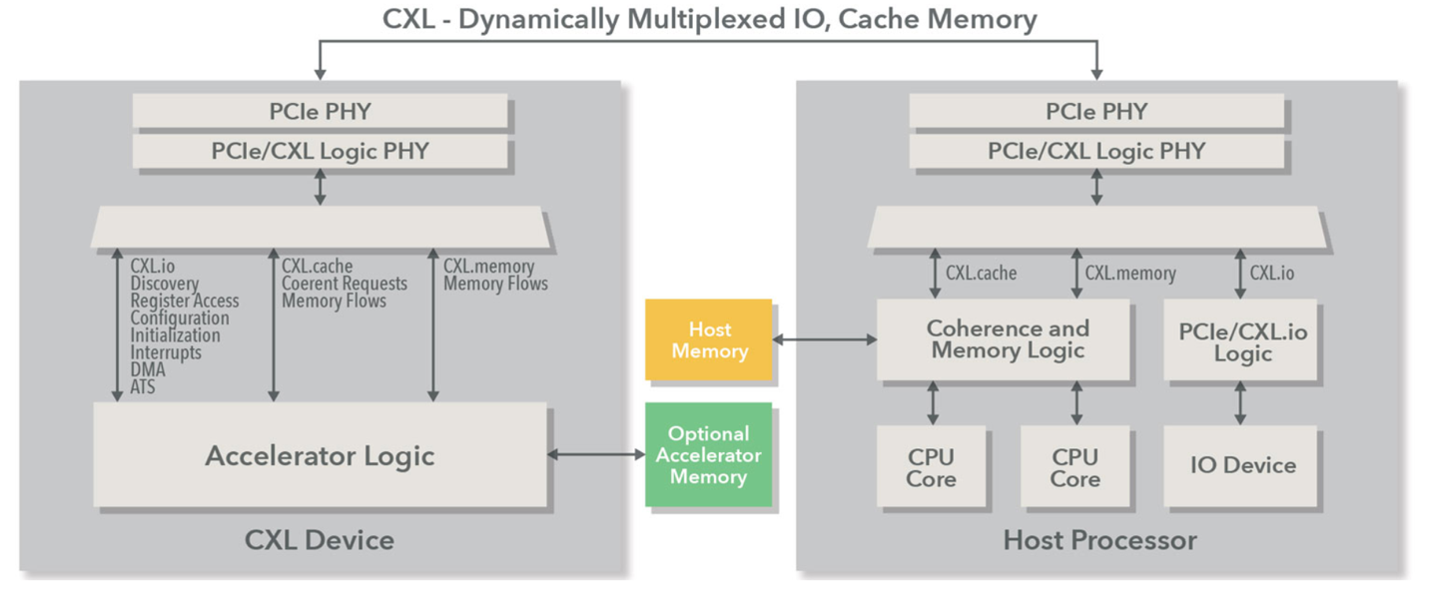

As an Intel-initiated standard, CXL layers on top of PCIe (as does NVMe, but that’s another story). PCIe already provides the physical interface standard, also the protocols and traffic management for IO communication. CXL builds on top of this for memory and cache communication between devices. This makes it a complex protocol to verify out of the gate, requiring PCIe compliance just as a starting point.

CXL layers on top of PCIe three protocols:

- io for configuration and a variety of administrative functions

- cache providing peripherals with low-latency access to host memory

- memory allowing the host to coherently access memory attached to attached CXL devices

The coherency requirement adds more complications such as compliance with the associated coherency protocol (eg MESI). Also add in Integrity and Data Encryption (IDE) to ensure secure connection and computing. Put all of this together and it is clear that CXL protocol checking is a very complex beast, for which a well-defined VIP would be enormously helpful.

Questa VIP for CXL

Siemens EDA have built a Questa VIP to address this need. QVIP can model any or all the CXL-compliant components in a system, including IDE, generating fully compliant stimulus in host, device, or passive device roles. The VIP comes with a comprehensive verification plan covering simple and complex scenarios. The VIP comes with predefined sequences to support generating these scenarios. Checkers are provided to validate compliance with the coherency protocol of choice, also to validate data integrity through cache reads, writes, and updates.

When a problem is found, possibly elsewhere in the system, the VIP provides detailed logging, from both device to host and from host to device. This logs all information on the CXL interconnect by timestamp, which simplifies tracking problems back to transactions. It is also possible to enable detailed debug messages. Once you know roughly where you want to look you can trigger detailed transaction information in both directions.

Finally, for coverage, the testplan supplied with the VIP is designed to guide you to high coverage over your CXL compliance testing. Table entries define the main test objective, and each objective comes with predefined coverpoints. You can tweak weights for these as appropriate to your verification goals. So, it’s an all-in-one package: VIP, testplan, debug support, and coverage. You just have to dial in your menu choices.

CXL looks likely to be the multi-chip/chiplet solution of choice for coherent memory sharing. This means that you should expect to see this play a larger role in verification planning. If you want to learn more about the Questa Verification IP solution, click HERE.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.