Digital designers have been automating the functional verification process for many years now, however when you talk to an analog designer about how they do verification you quickly realize that the typical process is quite ad-hoc and little automated. Necessity does create an opportunity so the software engineers at Methodicshave created a method to automate the analog simulation verification process when using the Virtuosoenvironment from Cadence. Vishal Moondhra from Methodics presented at CDNLive this month, and I’ve just reviewed his 23 slides.

An analog IC designer can benefit from circuit simulation and verification automation by:

- Repeatability – using scripts

- Parallelization – many tests finish quicker in parallel

- Tracking – a complete history of what is passing and failing

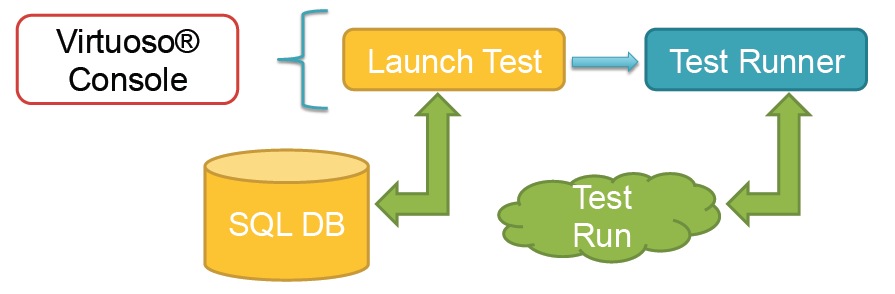

On the repeatability benefit, Methodics has created a runner script that launches a new circuit simulation, monitors the progress, reads the simulation results, then returns a Pass or Fail status. This new analog verification flow starts within the Virtuoso Console where you prepare your circuit schematic and input stimulus, launch your latest test and have the Pass/Fail results automatically saved in a database.

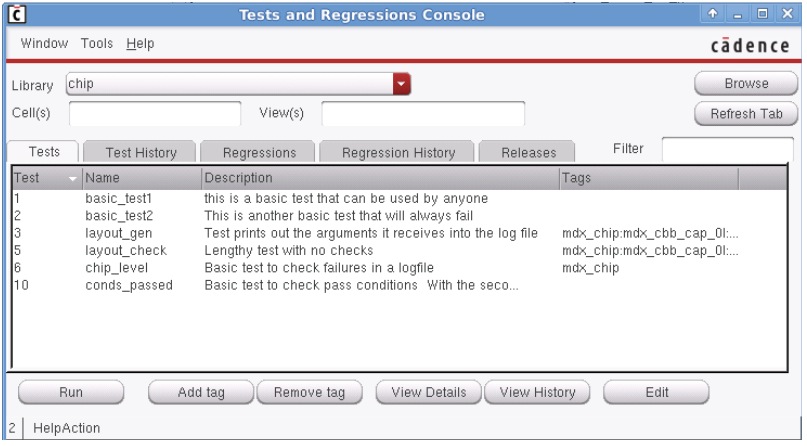

Within Virtuoso you get to see a list of tests available to run on your design, can launch these tests, and view the results of any test.

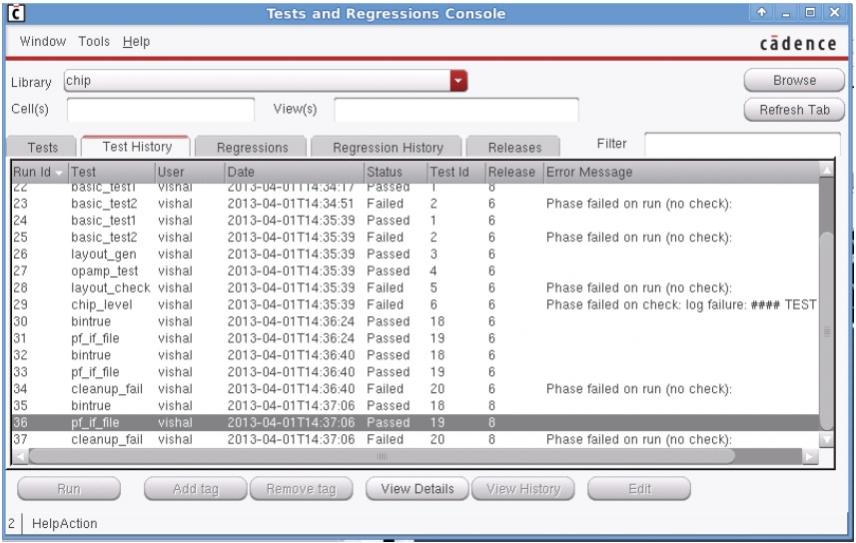

The tracking history is stored by Methodics in an SQL database and you can tell when a regression was started, finished, it’s Pass/Fail status and some other statistics. Good bye ad-hoc, hello automated methodology.

When reviewing test results you can filter the tests by: Library, Cell or View strings. This helps you get to just the need results instead of seeing all test results.

All of these new capabilities are an add-on to the Methodics product VersIC and you can use any circuit simulator in Virtuoso: Spectre, HSPICE, BDA, Eldo, etc. The base technology came from Evolve, a digital test and regression management framework acquired by Methodics in 2012.

Summary

Analog verification of circuit simulation results can now be automated instead of using ad-hoc and manual techniques, which will certainly save you some time. IC designers with Cadence Virtuoso can control and track their analog simulation verification progress in a familiar GUI. All of the test results are automatically saved for you in a database. This new automation approach from Methodics is a step in the right direction for transistor-level IC designers.

Related Blogs

- Bringing Sanity to Analog IC Design Verification using Regressions

- Analog IC Verification – A Different Approach

lang: en_US

Share this post via:

Comments

0 Replies to “Automating Analog Verification in Virtuoso”

You must register or log in to view/post comments.