Successful projects leverage the investment in comprehensive methodology and resource planning, covering design and analysis flows – that planning effort is especially important for functional verification.

The emergence of complex SoC designs for advanced automotive applications has led to a major focus on verification planning, as reflected in the ISO26262 standard. This standard defines requirements for automotive product verification, specifically:

- traceability to specifications

SoC design specifications correspond directly to verification targets – testbenches are established that link to each specification.

- scope of design functionality

Verification testbenches are required to demonstrate the design does not contain unintended functionality.

- identification and verification of failure modes

Testbenches are defined to verify the design response to a failure.

- integration of model components

As model component testing is completed, component integration into the full system model commences. The verification plan defines the integration tests developed to demonstrate correct component interaction.

These testbench plans will also commonly incorporate (embedded) software code, whose development cycle runs concurrently with the SoC design schedule.

Advanced system designs – especially automotive systems – incorporate a rich mix of digital and analog components. The verification strategy for analog components has several unique facets. Whereas digital verification explores model functionality, analog simulations focus on performance measures. Digital verification is primarily based on batch job regressions, whereas analog blocks are evaluated using a mix of interactive and batch simulations. Analog block verification is typically the direct responsibility of the design engineer, working within a tool “cockpit”. This is fundamentally different from digital verification, which primarily uses a mix of (software and hardware accelerated) simulation and formal methods.

Yet, the nature of advanced (mission-critical) system applications necessitates that verification planning extends to the analog design environment, as well – i.e., traceability to performance requirements, analysis across numerous operating modes, and sub-component integration. In short, analog block verification planning is as crucial to overall project success and compliance to product development standards as digital verification planning.

I recently had the opportunity to chat with some colleagues at Cadence Design Systems, to learn how they are supporting the breadth of project verification planning tasks. Larry Melling, Director of Product Management for the System Verification Group, initially provided some background. Larry said, “Cadence developed the vManager product, to address the need for an overall ‘umbrella’ to the overall verification planning and tracking activity. This top-level environment provides the necessary links between specifications and testbenches. vManager incorporates features to submit functional regressions, analyze failing tests, and rerun individual tests with additional signal tracing.”

Larry continued, “As verification utilizes an incremental, continuous integration flow, vManager works with source control management tools and model history data to optimize regressions – if model components are unchanged, associated regression testbenches need not be submitted. The vManager traceability to functional requirements provides a full coverage-driven view of the project verification status.”

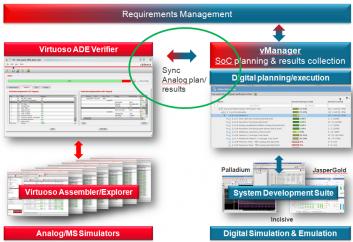

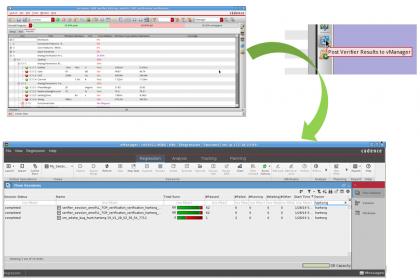

A figure depicting vManager utilizing data from Cadence functional simulation products in appended below. The digital simulation (and formal) tools provide functional verification data to vManager (on the right-hand side of the figure), whereas the left-hand side of the figure illustrates the link to analog verification.

(Also, please see an earlier Semiwiki article on vManager – link.)

Steve Lewis, Director of Product Management for the Custom IC and Packaging Group, added, “The Analog Design Environment product suite is the heart and soul and analog block design and simulation. Due to the unique nature of ADE compared to functional verification, we knew a bridge to the overall vManager environment was needed, providing a consistent project status view. The ADE Verifier feature is the ‘Golden Gate Bridge’ between the functional verification environment(of Marin County) and the ADE simulation environment(the city of San Francisco).”

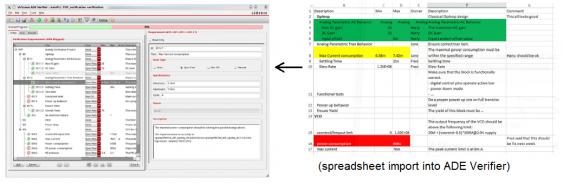

Walter Hartong, Product Engineering Architect in the Custom IC and Package Group, expanded upon some of the technical capabilities of ADE Verifier. “Analog block designs have traditionally been developed with rather ad hoc methodologies toward verification planning. ADE Verifier helps the designer to formalize analog performance requirements, with pass/fail measurement ranges for block specifications. Design groups can import their verification plan from other sources to help getting started with ADE Verifier.”

“As analog blocks commonly evolve in a mix of top-down and bottom-up integration styles, leveraging the hierarchical design views in ADE was key.”, Steve indicated.

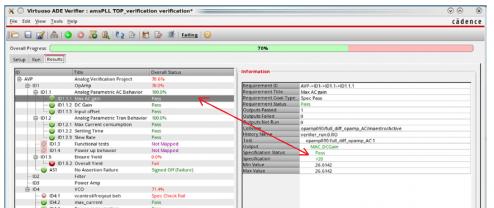

The figures below illustrates the ADV Verifier interface, and the import of an initial verification plan from an (unstructured) spreadsheet. The verification plan hierarchy is also highlighted.

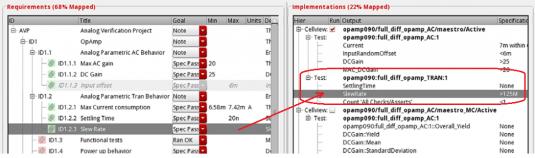

“After the block specifications are captured, the key step in ADE Verifier is ‘mapping’ the requirement to a design verification testbench. The(one-to-one or one-to-many) mapping indicates that the product requirement will be fulfilled by the selected testbench measure(s).”, Walter continued.

The figure below illustrates the ADE Verifier interface for mapping requirements to simulation measures – note that the tree structure of the design hierarchy is part of the mapping linkage. ADE Verifier also tracks the simulation requirements across environment conditions (PVT corners) and operating modes.

Walter indicated, “An additional benefit of adopting ADE Verifier for analog block verification planning is the direct applicability to IP reuse. Most analog designs evolve through multiple variants – a verification plan for an existing design provides a starting point for the development of a block revision.”

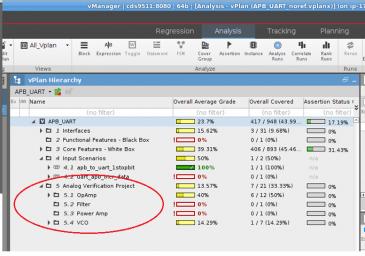

As mentioned above, a key benefit of verification planning is a concise, consistent, and accurate view of the block status. As ADE Verifier is bridges to the vManager database, project-wide reporting status is readily available – the figures below illustrate the upload of ADE Verifier data to vManager, and the detailed results information available for each testbench.

Structured verification planning has become de rigueur for project managers, providing traceability between system specifications and the associated testbench(es). The unique nature of analog block design requires a specific (cockpit-based, metric-driven) approach to verification planning, as exemplified by ADE Verifier. Further, a “bridge” is required to consolidate digital (functional) and analog (performance) verification status, as embodied in vManager.

For more information on these approaches, here is a product link and a link to a very illuminating whitepaper.

-chipguy

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.