Software-centric Emulation environment takes the forefront in modern SoC verification. As more and more devices are IoT enabled, the SoCs have to make special provisions to factor many things including communication, power usage, and network switching, and so on. Also, the demand for an SoC (specifically for smartphone which is pivotal for IoT) to handle multiple functions pertaining to audio, video, data, mobile etc. increases the size and complexity of the SoC significantly. Considering the three connection points for IoT; endpoint, gateway and cloud, the complexities of chipsets increase in that order. An SoC for cloud (data center) application, or even for gateway application has to handle what we call “Big Data” coming from multiple sensors from all connected devices through the system.

Traditional verification methods such as simulation with testbench approach or even traditional in-circuit emulation (ICE) are not sufficient for verifying such SoCs. There is a need for a more robust, software-based, virtual emulation solution that is scalable, flexible with job sharing and remote access facility for multiple teams to work at a time, easy-to-use, and reliable without much cabling in the system.

By now we are aware of Mentor’sVeloce emulation system coming out of the closet for remote teams to run their live applications on it. During this year’s DAC, Mentor also announced Veloce’s integration with ANSYS’PowerArtist for advanced real-time power analysis early in the design cycle.

Let’s review Veloce in the context of an emulation data center and see how it addresses the key verification challenges of an IoT-centric SoC or any other mobile SoC for that matter.

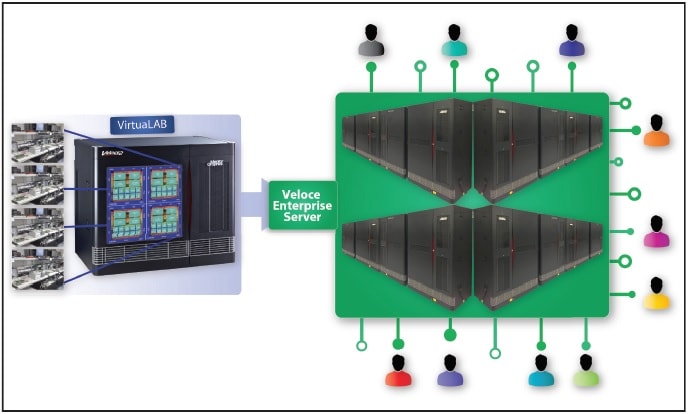

Veloce VirtuaLAB is a software-based virtual emulation data center with Enterprise Server capability that requires only the emulator and workstations to execute the software versions of the protocol models. The emulator has a single operating system, Veloce OS for all applications (internal or third party) to run on it. The Enterprise Server optimizes resource utilization and job sharing through LSF software.

Multiple users from remote sites across the world can concurrently access this emulation system for multiple projects from their desktops. The VirtuaLAB models can be easily reconfigured by simply changing their compile parameters as required. Let’s see how this system addresses the five key challenges –

Protocol Solutions – Chips are accommodating increasing number of protocols. Veloce offers software-based solutions including host/peripheral models, protocol exerciser/analyzers, and software debug for multiple market segments such as mobile, networking, multimedia, and storage interconnect. These are mostly IP-based. It’s expected that the solution be extended for other popular IoT frameworks as well.

Larger Designs – Veloce provides a scalable platform for increasing sizes of SoCs – Quattro for up to 256 million gates / system and up to 16 users; Maximus for up to 1 billion gates and up to 64 users; Double Maximus for up to 2 billion gates and up to 128 users.

Lower Power – Veloce can boot the OS and run billions of cycles to fully exercise live software applications running on the target hardware. As said above, third party power analysis tools such as PowerArtist can be integrated with Veloce to get accurate power analysis numbers for real applications early in the design flow. This is a unique capability of Veloce.

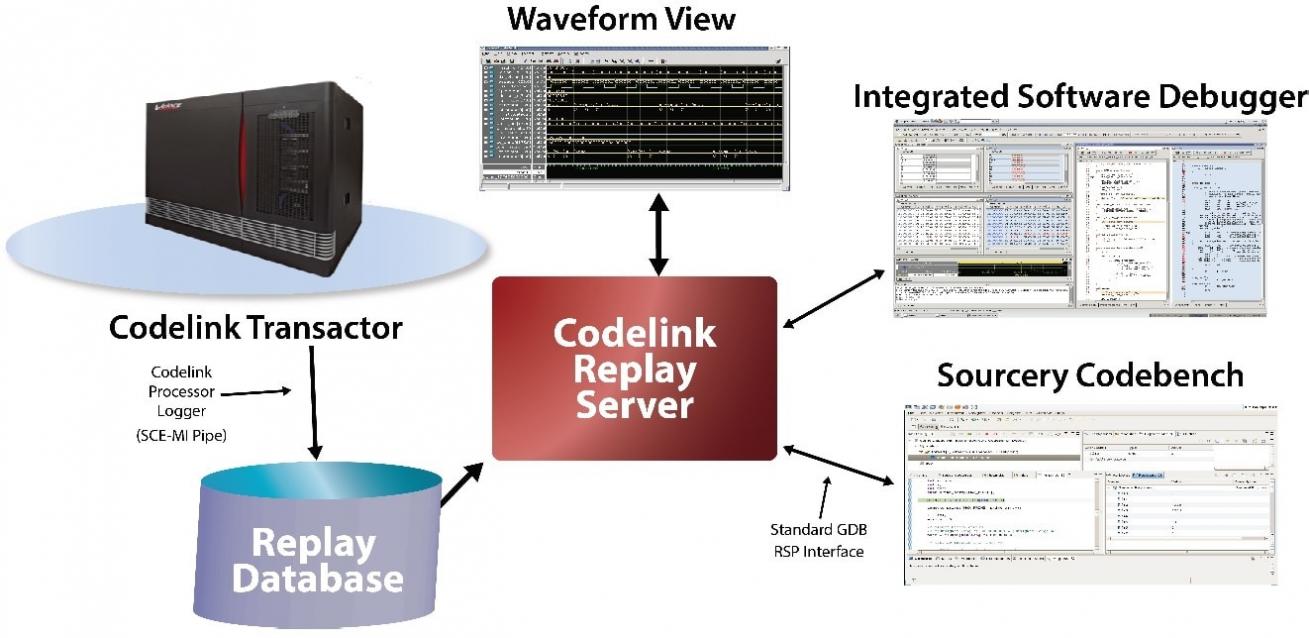

Debugging large software content – The software in IoT context can be varied for edge, gateway, and cloud. Veloce provides a virtual environment where different applications can run on the same Veloce OS. Virtual Probes which provide virtual connection with the software debugger are used for live interactive debugging.

When the emulator is off, Veloce Codelink supports offline and re-playable debugging for multiple, concurrent users. Multiple databases are generated by the emulator which can be used offline for debugging, thus freeing up the emulator for other tasks and users.

Network Switch and Router Ports – In IoT applications an SoC can have thousands of ports making it impossible to provide connections in hardware test environment. Veloce VirtuaLAB provides most of the test environment into software where the emulator is connected to the user environment on a workstation through one or more software connections that enable the user to interact with the DUT running in the emulator. As an example, for Ethernet, there is Ethernet Packet Generator and Monitor (EPGM) application that runs on the workstation to generate virtual Ethernet traffic and provide visibility, analysis, and user control of the traffic.

The Veloce virtual emulation data center is a step in the right direction to support massive amount of verification needed to design the products and networks for IoT world. It provides better reliability, scale of operation with multi-user environment and remote access, lower cost of operation, and better quality with higher debug visibility in a software-based environment.

More details can be found in a whitepaper written by Richard Pugh on the Mentor Graphics website HERE.

Also read: Power Analysis Needs Shift in Methodology

Pawan Kumar Fangaria

Founder & President at www.fangarias.com

Comments

There are no comments yet.

You must register or log in to view/post comments.