In the early days an IC had a single clock and a single reset signal, making it a simple matter to reset the chip into a known, stable state, so there was little need for detailed analysis. For modern designs there can be dozens to hundreds of clocks, creating separate domains and some use of asynchronous resets, so the challenge of ensuring proper reset logic has become quite complex. If the reset tree has any logic errors, like metastability, glitches or functional failures, then a costly design spin cycle ensues. I’ve read a white paper from Siemens on this topic and share my insights for this blog.

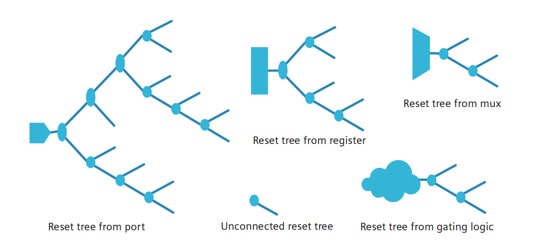

A Reset Domain Crossing (RDC) tool performs static verification to prevent unpredictable behavior, so it first analyzes RTL code to find all the reset logic, then classifies each reset:

- Synchronous or asynchronous

- Active high or low

- Set or reset

Static analysis further identifies the type of reset tree and its control flow.

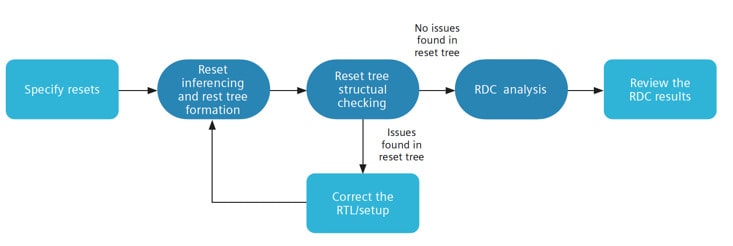

Siemens proposes an advanced structural check for a thorough RDC verification.

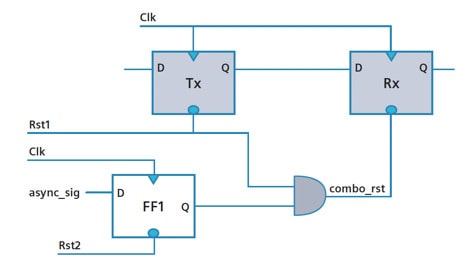

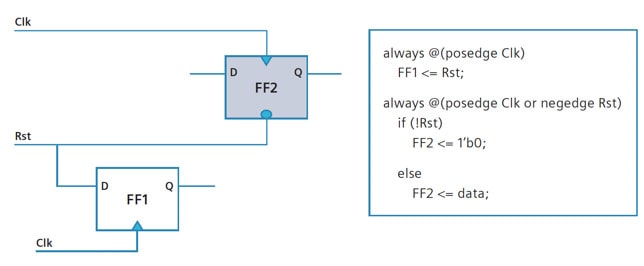

Consider the case where an asynchronous signal merges with a reset signal before reaching the register, signal FF1 may cause a glitch in the reset path.

An RDC path is flagged between register Tx and Rx, caused by signal combo_rst. Your design team then fixes the error by changing the reset domain to make it synchronous with the reset signal or by specifying a constant or a stable signal on the asynchronous signal.

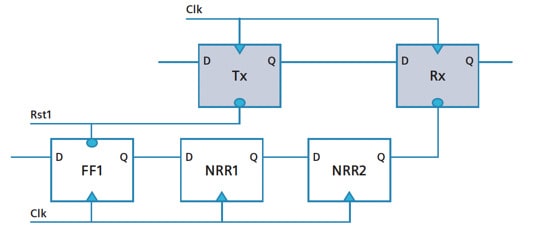

Non-resettable registers (NRR) on asynchronous reset paths may lead to an RDC issue in the reset path of Rx:

Questa RDC has a reset integrity check that identifies logic on NRRs, then a design engineer fixes the metastability issue.

If an asynchronous reset signal Rst is also used as data then it will create an RDC error, so the designer will be alerted to fix their RTL code to avoid this type of logic. If you really want this logic, then add a waiver to Questa RDC.

Case Study

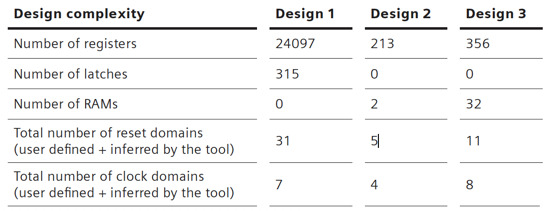

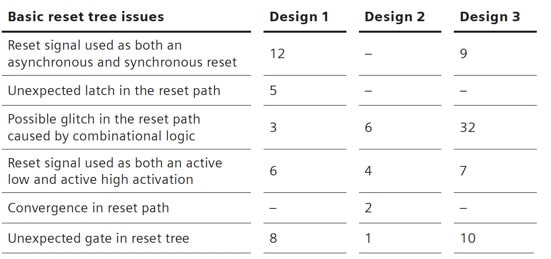

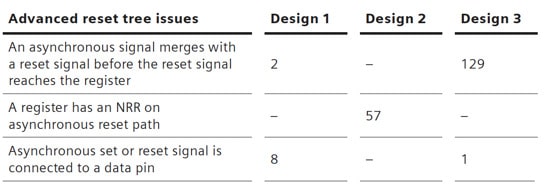

The Questa RDC tool was run on three designs of varying sizes and complexities to give you an idea of how the static analysis provides thorough feedback to RTL designers on basic and advanced reset tree issues.

Structural issues were found in each of the three designs caused by basic reset tree issues.

There were a wide range of advanced reset tree issues identified by RDC validation.

Summary

The Questa RDC verification approach is quite thorough, ensuring the integrity of the reset tree logic, avoiding subtle errors caused by metastability, glitches and functional bugs. Both basic and advanced RDC verification are required, so that design teams can fix errors before tapeout, ensuring the most reliable and safe operation of a new chip. The earlier that you find these RTL issues, the more solid your design becomes and the quicker your team learns about best RDC practices.

Read the entire 13-page white paper, Effective identification of reset tree bugs to mitigate RDC issues.

Related Blogs

- Automating Reset Domain Crossing (RDC) Verification with Advanced Data Analytics

- How to Find and Fix Soft Reset Metastability

- Automotive SoCs Need Reset Domain Crossing Checks

- Learning to Live with the Gaps Between Design and Verification

- Functional Verification using Formal on Million Gate Designs

- Caution: Reset Domains Crossing

Comments

There are no comments yet.

You must register or log in to view/post comments.