Lu Dai (chair of Accellera) and I had our regular chat at DVCon U.S. 2026. Accellera also hosted a reception in the exhibits hall, with free snacks and drinks, very well attended. We talked about what’s new in Accellera, with a particular emphasis on the recently released standard for CDC and RDC tool interoperability, also Lu’s … Read More

Tag: rdc

Reset Domain Crossing (RDC) Challenges

In the early days an IC had a single clock and a single reset signal, making it a simple matter to reset the chip into a known, stable state, so there was little need for detailed analysis. For modern designs there can be dozens to hundreds of clocks, creating separate domains and some use of asynchronous resets, so the challenge of ensuring… Read More

Automating Reset Domain Crossing (RDC) Verification with Advanced Data Analytics

The complexity of System-on-Chip (SoC) designs continues to rise at an accelerated rate, with design complexity doubling approximately every two years. This increasing complexity makes verification a more difficult and time-consuming task for design engineers. Among the key verification challenges is managing reset domain… Read More

Getting to Faster Closure through AI/ML, DVCon Keynote

Manish Pandey, VP R&D and Fellow at Synopsys, gave the keynote this year. His thesis is that given the relentless growth of system complexity, now amplified by multi-chiplet systems, we must move the verification efficiency needle significantly. In this world we need more than incremental advances in performance. We need… Read More

Automotive SoCs Need Reset Domain Crossing Checks

When the number of clock domain crossings (CDCs) in SoCs proliferated it readily became apparent that traditional verification methods were not well suited to ensuring that they were properly handled in the design. This led to the creation of new methods and tools to check for correct interfaces between domains. Now, in automotive… Read More

Structural CDC Analysis Signoff? Think Again.

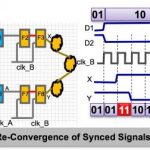

Talking not so long ago to a friend from my Atrenta days, I learned that the great majority of design teams still run purely structural CDC analysis. You should sure asynchronous clock domains are suitably represented in the SDC, find all places where data crosses between those domains that require a synchronizer, gray-coded FIFO… Read More

Design Perspectives on Intermittent Faults

Bugs are an inescapable reality in any but the most trivial designs and usually trace back to very deterministic causes – a misunderstanding of the intended spec or an incompletely thought-through implementation of some feature, either way leading to reliably reproducible failure under the right circumstances. You run diagnostics,… Read More

RDC – A Cousin To CDC

In a post-silicon bringup, it is customary to bring the design into a known state prior to applying further testing sequences. This is achieved through a Power-on-Reset (POR) or similar reset strategy which translates to initializing all the storage elements to a known state.

During design implementation, varying degrees of… Read More

Caution: Reset Domains Crossing

Because you can never have too much to worry about in verification, reset domain crossings (RDCs) are another hazard lying in wait to derail your design. Which hardly seems fair. We like to think of resets as dependable anchors to get us back on track when all else fails, but it seems their dependability is not absolute, especially… Read More

Domain Crossing Verification Needs Continue to Grow

Clock domain crossing (CDC) analysis has been around for many years, initially as special checks in verification or static timing analysis, but it fairly quickly diverged into specialized tools focused just on this problem. CDC checks are important because (a) you can lose data or even lock up at, or downstream of a poorly-handled… Read More