There’s no question that chip designs are getting more complex, driven by the power, performance, and area (PPA) demands of applications like artificial intelligence (AI), automotive, and cloud computing. This complexity, of course, trickles down to the design and testbench code. When engineers can find and fix bugs before sending their code to downstream simulation, emulation, and implementation tools, that makes the whole design process that much more efficient.

How can you generate correct-by-construction code for a more productive chip design and verification process? Let’s explore how in this post, which was originally published on the “From Silicon to Software” blog.

While typing a document, functions like auto-correct and spell checking make it more efficient to generate a clean copy. What if writing SystemVerilog code for your chip design was just as efficient? As hardware description and hardware verification languages go, SystemVerilog is one of the most commonly used. However, it also happens to be an extraordinarily complex language, with RTL constructs, assertions, and support for object-oriented programming and constrained-random testbenches. Designers have to fully compile and elaborate their SystemVerilog code, allowing connection of all parts of their design and testbench and also enabling complex checks.

Much like the software development process, with RTL code for chip designs, it’s best from a time and cost perspective to address bugs before they become costlier and more time-consuming to fix later in the design process. In an ideal world, designers would catch as many types of problems as they can while entering their RTL. Verification engineers would do the same while coding their testbench. When teams are able to deliver correct-by-construction code, this is much like a shift left in the software world—and in this case, the resulting productivity lift accelerates the design and verification process.

Traditional Verification Can Be Labor Intensive

Traditionally, SystemVerilog or Universal Verification Methodology (UVM) testbench are only verified after handoff to simulation or emulation—a time-consuming and labor-intensive process. Sometimes, unoptimized testbench code in proprietary or off-the-shelf verification IP (VIP) can create performance bottlenecks for simulation. Similarly, RTL code is verified with linting or static verification tools after RTL handoff at the module level. However, sub-systems or SoCs are typically verified much later in the design cycle or overnight through lint regressions. The next day, the designer for each module would have to resolve the issues detected and run the tools again, repeating the process until all issues detected have been resolved. Further along the process, a synthesis, emulation, or static timing analysis tool could also catch issues. But by then, fixing those problems would involve many costly iterations. Plus, different tools in the design flow support different language-related constructs, and any syntax errors at a later stage could be very time consuming.

Another consideration is the increasing complexity of today’s chip designs, along with the fact that these designs are developed by teams that are typically distributed in different locations around the world. These trends have made RTL descriptions imperative for handling designs with millions or even billions of gates, while hardware verification languages are making sophisticated verification possible using testbenches with pseudo-randomized stimulus and self-checking of results. However, the process of integrating all of the RTL code modules—without error—can be a Herculean task. What if there are missing signals? What if there’s a missed connection at the sub-system or SoC level? Every aspect of the design must be explored, yet the modify-compile-run cycle for design and testbench code is a lengthy one that can get further stalled by even minor bugs.

The Keys to Writing Cleaner Code

What’s needed to write cleaner code—and to do it faster? A tool that works much like the auto-correct and spell-checking capabilities in word-processing programs. Ideally, such a tool would:

- Perform full parsing of SystemVerilog code, down to the last parameter

- Provide the parsing, compilation, elaboration, and synthesis while the user is typing in the code

- Analyze signals at the bit level, detect dead code, and recognize clocks and resets

- Suggest quick fixes for the user to consider applying as is or modifying before using

- Be customizable to support a particular design or verification flow

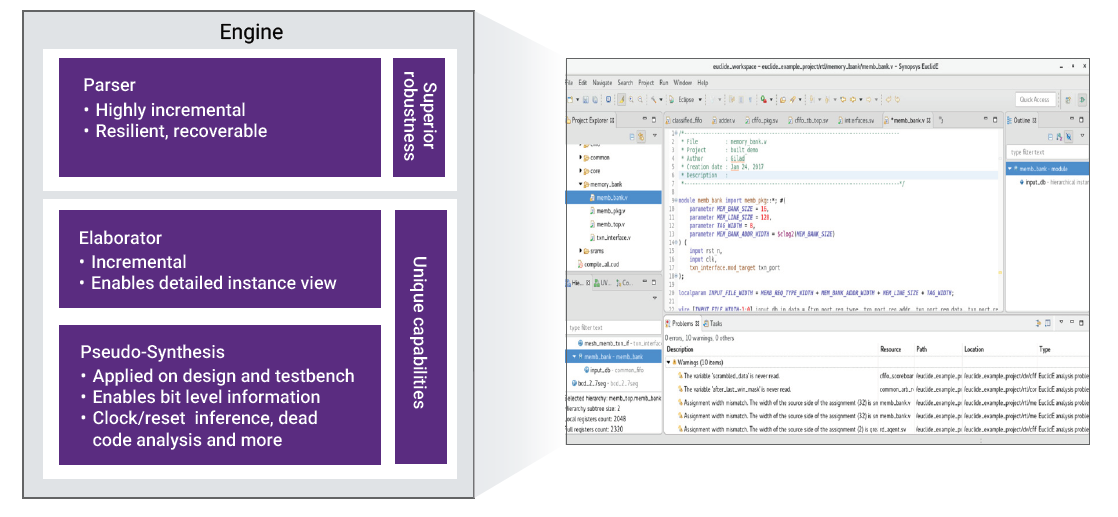

To foster the on-the-fly code correction that can enhance design and verification productivity, the new Synopsys Euclide solution provides the capabilities we’ve just outlined. Built by RTL experts, the solution identifies complex design and testbench compliance checks during SystemVerilog and UVM development. Thanks to its advanced algorithms, the Synopsys Euclide solution fosters high-performance compilation, elaboration, and pseudo-synthesis to deliver real-time feedback to enhance design and testbench quality during code development. By comparison, with traditional flows, users have to wait up to an hour or longer after typing in their code before they’re alerted to any errors. Other tools typically notify users of only one or two errors at a time before needing to be run again, while the Euclide solution is quite resilient and can proceed forward with incomplete and even broken designs to report as many errors as possible. This error recoverability is unique and provides advanced feedback on incomplete code. Synopsys Euclide also has a very fast incremental compilation engine and is executed as the user types in code, providing almost instantaneous feedback.

This diagram displays the Synopsys Euclide architecture and GUI.

Watch the Synopsys Euclide solution in action in these two short videos. The first video highlights how the tool performs linting and cleaning of code from violations during coding.

[Will embed “Better RTL and Testbench Code with Synopsys Euclide” here]

The second video shows features including content assist, automatic code generation, semantic coloring, and the design hierarchy tree.

[Will embed “Coding Testbench & RTL Using Synopsys Euclide” here]

Getting the Most Out of Downstream Design Tools

The context-specific auto-completion and content assistance capabilities of the Synopsys Euclide tool are tuned for the Synopsys VCS® functional verification, Verdi® automated debug, and ZeBu® emulation solutions and are compatible with Synopsys RTL and design synthesis solutions. Because of this, Euclide can provide feedback on areas such as simulation performance, emulation, and synthesis compliance checks. In fact, any simulation, emulation, formal, or synthesis tool should compile much smoother if the design, assertions, coverage, or other testbench collateral have been developed with the Euclide solution.

To test-drive the tool, you can download a 30-day trial of the Synopsys Euclide solution.

In our Smart Everything world, chip designs will only continue to grow more complex to meet the needs of innovative applications that are changing how we live, work, and play. By identifying and resolving bugs in design and testbench code early, you can avoid unnecessary simulation or synthesis cycles, long debug sessions, and costly chip re-spins as you push to get your products to market swiftly.

By Alex Potapov, Distinguished Architect, and Kiran Vittal, Sr. Product Marketing Director; Verification Group, Synopsys

Also Read:

Upcoming Virtual Event: Designing a Time Interleaved ADC for 5G V2X Automotive Applications

Optimize RTL and Software with Fast Power Verification Results for Billion-Gate Designs

Driving PPA Optimization Across the Cubic Space of 3D IC Silicon Stacks

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.