Over the years SerDes (serializer/deserializer) based connections have proliferated into just about every connection within and among computing systems. Years ago, parallel interfaces were the most common method of moving data, but issues of signal integrity, synchronization and power simply became too much for the required data rates. One by one old parallel links have been updated to modern serial connections. Remember parallel printer cables, ATA & IDE, or PCI connectors, to name a few? These have all been updated to serial equivalents and even on-chip connections between blocks have adopted network on chip architectures that rely on high speed serial links for moving packetized data.

The new age of USB, PCIe, NoC, ever faster memory, network and device interfaces have pushed SerDes designs into challenging high-speed realms. A single serial link carrying what used to be carried by a set of parallel wires needs to run that much faster. Add to it packetization, error correction and encoding and the speed requirements for SerDes become substantial.

All of these factors have made SerDes design critical for every market, including networking, IoT, automotive, servers, etc. One of the biggest challenges is verification with simulation. Modern SerDes have a mixture of digital and analog, thus making it impractical to run analog and/or digital simulation independently. Mentor, a Siemens Business, has recorded a webinar that breaks down the issues and potential solutions for SerDes simulation. In the video titled “Addressing Analog Mixed-Signal Verification Challenges of High Speed SerDes”, Scott Guyton, Solution Architect Manager in the Mentor AMS BU discusses all the facets of this issue.

Scott begins by summarizing the need for widely deployed high speed SerDes throughout electronic products. As mentioned above, all the major markets need increasing rates of data transfer and processing power. Some of the design challenges for these systems are clock and data recovery, dealing with high db loss & crosstalk, low power operation and support for multiple current and legacy protocols. Scott talks about how these system level challenges translate into SerDes circuit design challenges. High data rates call for stringent jitter and phase noise requirements. High channel loss necessitates equalization architectures and increased design complexities.

SerDes are not immune to issues found in advanced nodes. Long gone are the days where an interface SerDes could stay on an older process while the core moved to a new node for performance or capacity. SerDes designs also have to wrestle with clock domain crossings, programmable parameters and complex data paths. All of this this must be done while maintaining tight design margins.

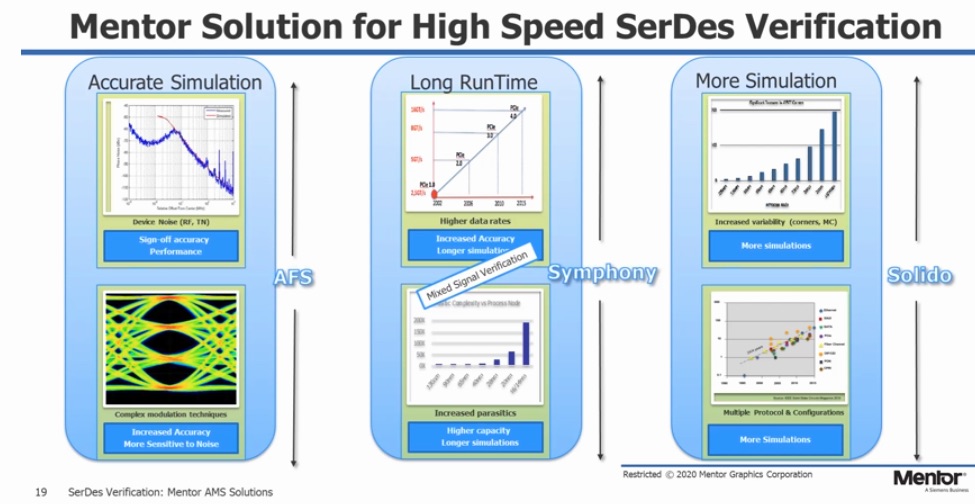

Mentor has assembled a comprehensive simulation solution that addresses the digital, analog and mixed signal domains needed for SerDes design. Scott reviews the requirements in the webinar. He divides them up into Performance, Accuracy, Capacity and Ease of Use (PACE). Analog simulation is used for transient, transient noise and RF. Mixed signal needs to maintain SPICE accuracy and allow for sufficient cycles of digital or channel model to validate the design. Digital simulation covers corners and Monte Carlo to assure yield and help with design optimization.

Mentor offers their Symphony Mixed Signal Platform, which is powered by AFS and can integrate with a wide range of industry standard HDL simulators. Symphony lets designers switch between analog, digital and behavioral models to trade off performance or accuracy, as needed. With AFS, runtimes are dramatically shortened to allow more simulations in a smaller period of time.

Scott closes the webinar with a set of case studies showing how their customers took advantage of the Mentor simulation platform. The first case study includes information on simulation accuracy versus measured silicon at 7nm for SerDes intended for automotive and IoT applications. The second case study is a specially designed SerDes for use in a GPU interface PHY. The customer was able to run a mixed signal simulation at high accuracy with fast runtimes using Symphony. The third case study was a SerDes for 5G and automotive. Symphony solved the customers convergence issues while improving accuracy and runtime. The last case study covers variation aware verification for level shifters in a large design. The design had hundreds of level shifters and they needed to verify that they all would work over all PVT cases. Mentor’s Solido PVTMC made this possible with only 2713 simulations instead of the 9.7M required for brute force.

The webinar is filled with much more information than can be provided here. If you want to view the entire presentation, it can be found on the Mentor website along with the supporting material cited in the webinar.

In writing this article, Mentor provided me with a list of educational resources that may prove useful:

Mentor, together with Siemens Digital Industries Software, are offering special resources to help you make the best of this challenging time, including Free 30-Day On-Demand Training and a Free 12-month licenses of PADS Pro Student Edition.

If you’re interested in Mentor’s other webinar and virtual seminar offerings, check out:

- AMS Verification webinar series

- Catapult High-Level Synthesis Live Virtual Seminar: How to Use HLS to Optimize Your AI/ML, Vision and Smart IoT Applications for Performance and Power/Energy

- What’s New in Functional Verification online seminars

- The MEMS Digital Twin Flow webinar

- Tessent DFT webinar series

- Veloce emulation webinar series (upcoming in June)

Comments

There are no comments yet.

You must register or log in to view/post comments.