IC designer Shubhyant Chaturvediof AMD used EDA tools from Mentor Graphicsand Concept Engineeringto perform static, low-power verification of a mixed-signal SoC design with a combined CPU and GPU. Shubhyant presented a poster session at DAC two weeks ago in Austin, and I wanted to share it with my readers here at SemiWiki.

PROBLEM STATEMENT

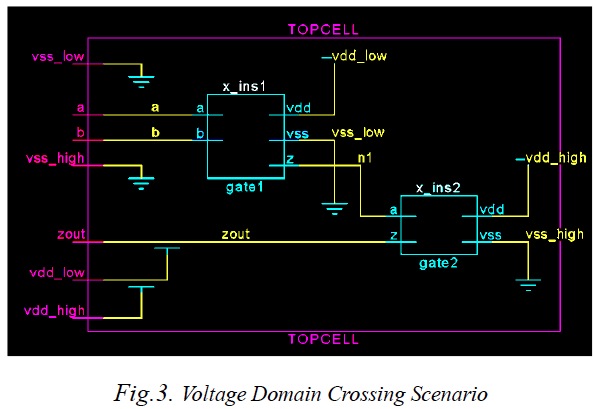

• Quite common to have signals traversing through multiple power domains across mixed-signal design boundaries in SoC.

• Low-Power Verification EDA Tools based on UPF (Unified Power Format) or CPF (Common Power Format) lack the capability to extend into transistor level logic of mixed-signal IPs [which may not be std-cell based].

• Mixed-signal IPs are therefore verified independently using Electrical Rule Checkers (ERC) .

• Black-Box Models of such IPs are then provided to SoC with power-properties assigned to interface pins.

• Assignment of properties and verification of assumptions behind those properties is often an error-prone manual task.

• Therefore a need for flat and efficient static verification methodology to check mixed-signal design interfaces.

• A static approach helps in bypassing issues related to dynamic verification such as dependency on completeness and correctness of test-vectors and capacity issues on large netlists.

FIREWALLING

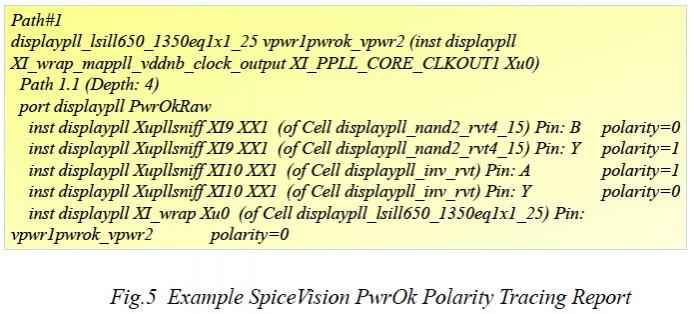

• A global control signal – PwrOk is used as a dominant isolation/firewalling control signal to all isolation cells/level-shifters

• PwrOk indicates that all voltage rails on the chip have reached initial values.

• Other power management control signals influencing power-states are logically AND-ed with PwrOk such that PwrOk stays dominant.

• Imperative for PwrOk to maintain its dominance and polarity throughout the combinatorial distribution path to avoid firewalling hazards.

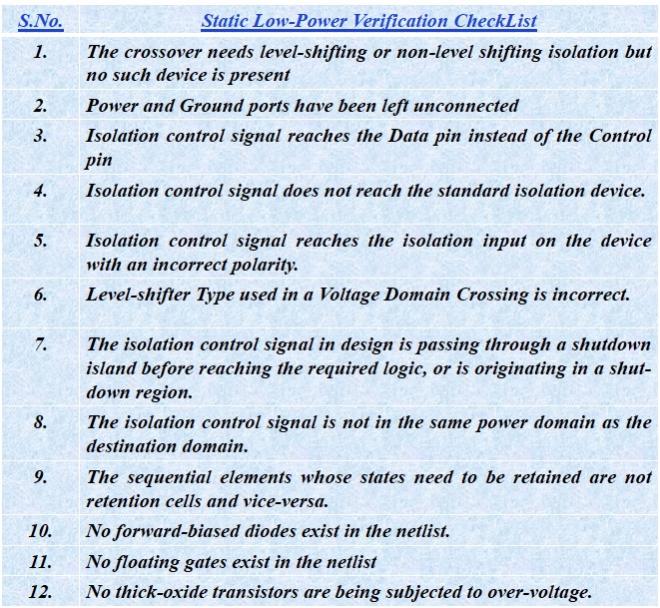

STATIC LOW-POWER VERIFICATION CHECKLIST (Key Checks)

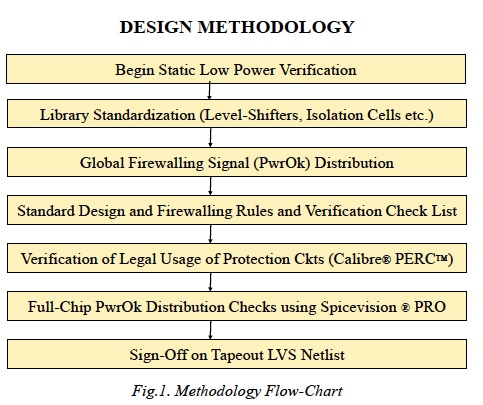

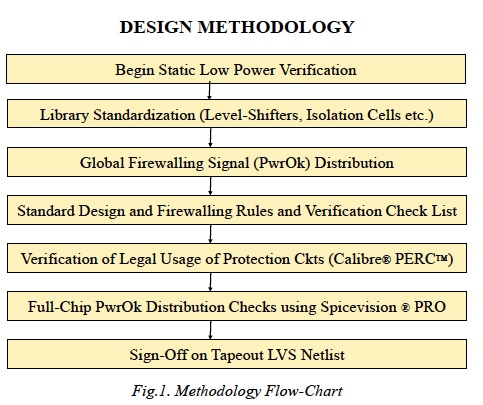

Methodology

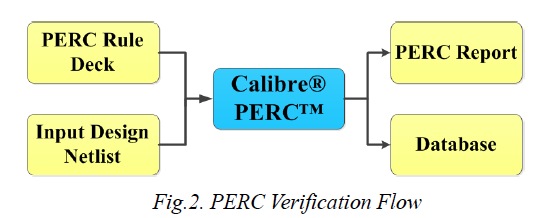

Calibre® PERC™

• PERC works on transistor-level netlists and has embedded features like Spice pattern recognition and Static Voltage propagation.

• Process involves declaring all supplies in the design which are iteratively propagated up and down the circuit hierarchy until all voltages on all nets are known and stable.

• Voltage propagation is much faster than standard simulation and thus can work on complex large-scaled SoC circuits.

• For memory and run-time efficiency, PERC uses cell-signatures to prevent re-computation of cell voltages.

• Technology independent flow and needs to know only the type of the transistors.

• API in Tcl Verification format (TVF) can then be used to apply various structural checks from the checklist.

SPICEVISION®PRO

• SpiceVision is used for verification of PwrOk distribution.

• Neatly enumerates all power management control distribution paths by extracting and highlighting those paths as distinct cones of logic in a schematic viewer.

• Builds a hierarchical binary netlist database named ZDB to store all possible connectivity information.

• PwrOk polarity is statically propagated right from the chip input to all the isolation control and firewall pins using Boolean truth-tables to make sure it reaches with the right logic-sense.

CASE-STUDY

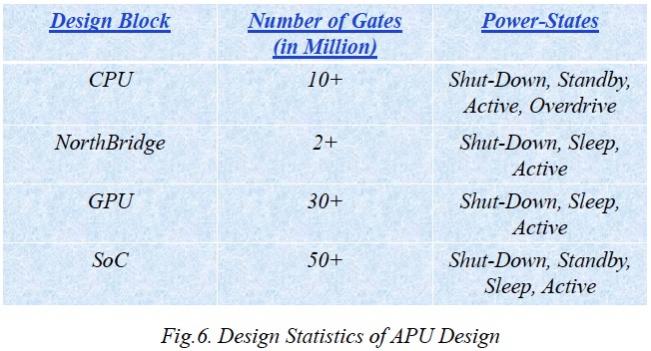

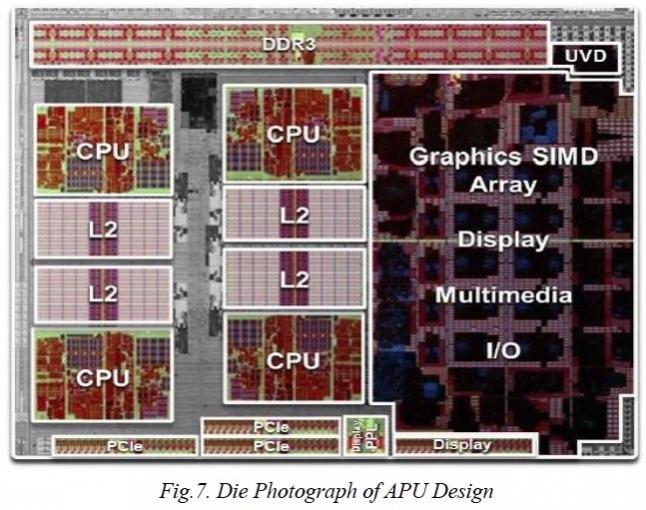

•Methodology was successfully deployed on an Accelerated Processing Unit (APU) Design which combines a Central Processing Unit (CPU) core and a Graphic Processing Unit (GPU) Core with six distinct power supplies on chip.

• Some key design errors which were masked in std flows got uncovered.

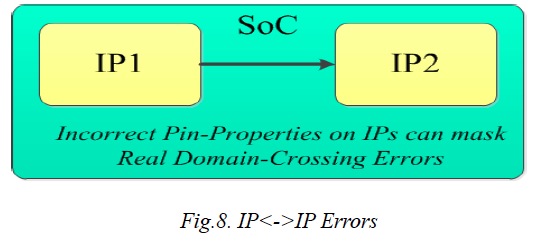

• IPIP Errors because of both IPs providing incorrect properties on pins.

•Errors found related to logical dominance and buffering of Firewall Signals on power-gated domain inside a Mixed- Signal IP which was black-boxed at SoC level.

• Errors found related to parasitic diodes getting forward-biased.

LIMITATIONS

• Methodology is LVS spice-netlist based and therefore early feedback in the design cycle is limited.

• Additional coverage is limited in designs having Third-Party Mixed-Signal IPs which only provide black-boxed views.

ACKNOWLEDGEMENT

Sincere thanks for their help and support to several AMD-ers including Richard Bryant, John Petry, Jim Montanaro, Feng Gao, Mahesh Sharma, Aaron Grenat, Brian Kasprzyk, Sreekumar Menon, Shitanshu Tiwari, Ramanan Balakrishnan, Anand Mishra, Raghavendra Kamath, Chris Peura, Kenny Chiu, Rajiv Hattangadi, Steve Kommrusch and Venkateswaran Govindarajan.

Further Reading

lang: en_US

Share this post via:

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?