Last week there was a meeting of the GSA Analog/Mixed-Signal (AMS) working group. It was completely focused on FD-SOI (I hate that name, especially since FinFET is also fully-depleted. I vote for BoxFETs.) It was a bases loaded meeting with presentations from ST Microelectronics (calling in from France close to midnight), Samsung… Read More

Jen-Tai Hsu Joins Kilopass and Looks to the Future of Memories

Kilopass has a new VP of engineering, Jen-Tai Hsu. I sat down with him last week to find out where he came from and where he and Kilopass are going.

He grew up in Taiwan and went to National Taiwan University where he studied electrical engineering. Then he came to the US and went to Case Western Reserve University to get a masters degree,… Read More

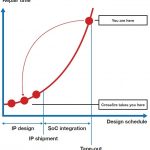

Foolproof Your IP before it Stumbles in Higher-up Design

SoC designs are increasingly becoming assemblies of a large number of IP blocks. A well integrated assembly can lead to a successful PPA (Power, Performance and Area) optimized design. However, it is equally important that each IP block is optimized, robust, and integrable in the design. The complexity of an IP and its integration… Read More

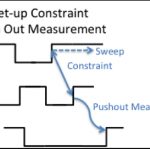

Ultra-low Voltage: Is Your Slack Really Positive? Are You Sure?

During synthesis and static timing the main figure of merit is “slack”. If a signal arrives with time to spare before it is needed (often measured against the setup time before a clock changes at a register) then the slack is positive. Positive slack is generally a good thing, although it can indicate over-design if … Read More

Acoustic Resonators for RF: MEMS with No Moving Parts

There is an annual conference known officially as the Sensors and Actuators Workshopand informally as Hilton Head since it is held on Hilton Head island in South Carolina. Coventor talked to some of the top researchers last year about RF filters and decided to develop a simulation solution that would better serve both the researchers… Read More

Why Modern SoC need cache-coherent NoC?

Launching high technology product on the semiconductor market after your competitors is not necessarily a weakness. NetSpeed has developed NocStudio, a front end optimization design tool helping architects to create SoC architecture bridging the gap with the back end, floor planning and place and route. Created about 20 years… Read More

UTBB SOI can scale down to 5nm says Skotnicki…

…and FinFET down to 3nm. This assertion is the result of extensive research work made by Thomas Skotnicki, ST Fellow and Technical VP, Disruptive Technologies, leading to numerous publications, like in 1988 in IEEE EDL or in 2008 in IEEE TED paper. I say extensive, I should also say long, very long, as it took almost 30 years for the… Read More

FD-SOI: a Gentle Introduction

Over the last couple of weeks, FD-SOI has been in the news with GlobalFoundries announcement of a 22nm FD-SOI process that will run in the Dresden Fab. Also, earlier in the week I talked to Thomas Skotnicki about the saga (and it is a saga) of how FD-SOI got from his PhD thesis to volume manufacturing and global deployment. But there … Read More

Thomas Skotnicki: FD-SOI 26 Years in the Making

It seems to be FD-SOI week yet again. I talked to Thomas Skotnicki this morning. He is the father of thin-box FD-SOI and its birth is an interesting story. The story began 26 years ago (so not quite as far back as the photo!).

Thomas is of Polish origins (he is actually Tomeczek) and grew up in Warsaw where he earned his PhD. In 1983 in Canterbury,… Read More

NetSpeed NoC IP or Architectural Synthesis Company?

When you look at NetSpeed’s NocStudio design tool, you first think “I see, NetSpeed is a new Network-on-Chip (NoC) IP company”. Are you wrong? Yes and no… No because NocStudio indeed generates a NoC. Yes, because the company objectives are going much farther than simply deliver a new NoC solution. According with Sundari Mitra, … Read More